Received June 3, 2020, accepted July 7, 2020, date of publication July 9, 2020, date of current version July 29, 2020.

Digital Object Identifier 10.1109/ACCESS.2020.3008250

# **Hardware-Accelerated Platforms and Infrastructures for Network Functions: A Survey of Enabling Technologies** and Research Studies

PRATEEK SHANTHARAMA<sup>101</sup>, (Graduate Student Member, IEEE), AKHILESH S. THYAGATURU<sup>®2</sup>, (Member, IEEE), AND MARTIN REISSLEIN [December 1], (Fellow, IEEE)

School of Electrical, Computer, and Energy Engineering, Arizona State University (ASU), Tempe, AZ 85287, USA

<sup>2</sup>Programmable Solutions Group (PSG), Intel Corporation, Chandler, AZ 85226, USA

Corresponding author: Martin Reisslein (reisslein@asu.edu)

This work was supported by the National Science Foundation under Grant 1716121.

**ABSTRACT** In order to facilitate flexible network service virtualization and migration, network functions (NFs) are increasingly executed by software modules as so-called "softwarized NFs" on General-Purpose Computing (GPC) platforms and infrastructures. GPC platforms are not specifically designed to efficiently execute NFs with their typically intense Input/Output (I/O) demands. Recently, numerous hardware-based accelerations have been developed to augment GPC platforms and infrastructures, e.g., the central processing unit (CPU) and memory, to efficiently execute NFs. This article comprehensively surveys hardware-accelerated platforms and infrastructures for executing softwarized NFs. This survey covers both commercial products, which we consider to be enabling technologies, as well as relevant research studies. We have organized the survey into the main categories of enabling technologies and research studies on hardware accelerations for the CPU, the memory, and the interconnects (e.g., between CPU and memory), as well as custom and dedicated hardware accelerators (that are embedded on the platforms); furthermore, we survey hardware-accelerated infrastructures that connect GPC platforms to networks (e.g., smart network interface cards). We find that the CPU hardware accelerations have mainly focused on extended instruction sets and CPU clock adjustments, as well as cache coherency. Hardware accelerated interconnects have been developed for on-chip and chip-to-chip connections. Our comprehensive up-to-date survey identifies the main trade-offs and limitations of the existing hardware-accelerated platforms and infrastructures for NFs and outlines directions for future research.

**INDEX TERMS** Central processing unit (CPU), hardware accelerator, interconnect, memory, software defined networking (SDN), virtualized network function (VNF).

# I. INTRODUCTION

A. TREND TO RUN SOFTWARIZED NETWORK FUNCTIONS ON GENERAL-PURPOSE COMPUTING (GPC) PLATFORMS

Traditionally, the term "network function (NF)" applied primarily to functions of the lower network protocol layers, i.e., mainly the data link layer (e.g., for the data link layer frame switching NF, virtual local area network NF, and medium access control security NF) and the network

The associate editor coordinating the review of this manuscript and approving it for publication was Junaid Shuja.

layer (e.g., for the datagram routing NF and Internet Protocol firewall NF). These low-level NFs were usually executed in specially designed dedicated (and typically proprietary) networking equipment, such as switches, routers, and gateways. Recently, the definition of an NF has been broadened to describe networking related tasks spanning from lowlevel frame switching and Internet Protocol (IP) routing to high-level cloud applications [1]-[3]. The area of networking currently undergoes an unprecedented transformation in moving towards implementing NFs as software entities so-called "softwarized NFs"—that run on General-Purpose

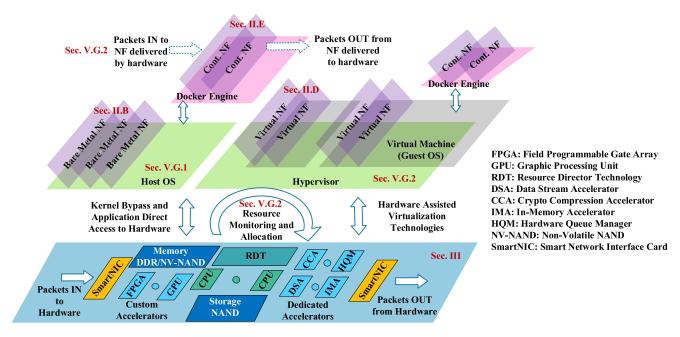

FIGURE 1. Illustration of GPC platform hardware to process Network Functions (NFs). An NF can be implemented as a Bare Metal NF, Application NF (not shown), Virtual NF (VNF), or Container NF (CNF).

Computing (GPC) platforms and infrastructures as opposed to dedicated networking equipment hardware.

In order to motivate this survey on hardware-accelerated platforms and infrastructures for softwarized NFs, we briefly introduce the basic concepts of softwarized NFs, including their computation and management on GPC platforms and infrastructures, in the following paragraphs. We then explain the need for hardware-acceleration of softwarized NFs on GPC platforms and infrastructures in Section I-B, followed by an overview of the contributions of this survey in Section I-C.

# 1) NETWORK FUNCTIONS (NFs) AND NETWORK FUNCTION VIRTUALIZATION (NFV)

The term "Network Function (NF)" broadly encompasses the compute operations (both logical [e.g., bitwise AND or OR] and mathematical scalar and vector [e.g., integer and floating point arithmetic]) related either directly or indirectly to data link layer (Layer 2) frames, network layer (Layer 3) datagrams or packets, and network application data (higher protocol layers above Layer 3). For instance, a packet filter is a direct logical NF that compares header data to allow or block packets for further processing, while a jitter and latency estimator function is an example of an indirect arithmetic NF. An NF that requires dedicated processing with a strict deadline, e.g., an NF to verify a medium access control (MAC) frame error through a Cyclic Redundancy Coding (CRC) check, is preferably implemented as a hardware component. On the other hand, an NF with relaxed timing requirements, e.g., TCP congestion control, can be implemented as a software entity.

The push towards "softwarized NFs" is to reduce the hardware dependencies of NFs for function implementation so as to maximize the flexibility for operations, e.g., to allow for the flexible scaling and migration of NF services. Softwarized NFs enable compute operations to be implemented as generic executing programs in the form of applications that can be run on a traditional OS or isolated environments, such as Virtual Machines (VMs) [4] or containers [5], on GPC platforms. Analogous to the broad term "Network Function (NF)", the term "Network Function Virtualization (NFV)" broadly refers to NF implementation as a virtualized entity, typically as an application (which itself could run inside a container), and running inside a VM (see Fig. 1). Thus, NFV is an implementation methodology of an NF; while the term NF broadly refers to compute operations related to general packet processing. Moreover, the term "Virtual Network Function (VNF)" refers to an NF that is implemented with the NFV methodology.

# 2) ROLE OF SOFTWARE DEFINED NETWORKING (SDN) IN THE MANAGEMENT OF NFs

Software Defined Networking (SDN) [6]–[9] is a paradigm in which a logically centralized software entity (i.e., the SDN controller) defines the packet processing functions on a packet forwarding node. The notion of centralized decision making for the function implementation and configuration of forwarding nodes implies that the network control plane (which makes the decisions on the packet processing) is decoupled from the network data plane (which forwards the packets). Extending the principles of SDN from forwarding nodes to the broad notion of compute nodes can achieve

more flexibilities in the deployment of NFs on GPC platforms in terms of scalability and management [10], [11]. More precisely, SDN can be applied for two primary purposes: *i*) macro-scale NF deployments, where the decisions involve selecting a specific platform for NF deployments based on decision factors, such as physical location, capabilities, and availability, and *ii*) micro-scale NF deployments, where the decisions involve reconfiguring the NF parameters during on-going operations based on run-time requirements, such as traffic loads, failures and their restoration, as well as resource utilization.

# 3) COMPUTE NODES FOR RUNNING NFs

In general, the compute nodes running the NFs as applications (VMs and containers) can be deployed on platform installations ranging from large installations with high platform densities (e.g., cloud and data-centers) to distributed and singular platform installations, such as remote-gateways, clients, and mobile nodes. The cloud-native approach [12] is the most common method of managing the platform installations for the deployment of NFs that are centrally managed with SDN principles. While the cloud-native approach has proven to be efficient for resource management in cloud and data center deployments of NFs, the applicability of the cloud-native approach to remote gateways, clients, and mobile nodes is yet to be investigated [13].

The wide-spread adoption of Multi-Access Edge Computing (MEC) [14] with cloud-native management is accelerating the trend towards softwarized NFs, which run on GPC platforms. The MEC aims to deliver low-latency services by bringing computing platforms closer to the users [15]–[19]. A key MEC implementation requirement is to inherit the flexibility of hosting a variety of NFs as opposed to a specific dedicated NF. A GPC platform inherently provides the flexibility to implement NFs as software entities that can easily be modified and managed, such as applications, Virtual Machines (VMs), and containers [20]. In a typical MEC node deployment, the GPC platform is virtualized by a hypervisor [21], e.g., Linux Kernel-based Virtual Machine (KVM), Microsoft HyperV, or VMware ESXi, and then NFs are instantiated as a VM or container managed by the hypervisor. The flexibility of an MEC is achieved by the process of migrating applications, VMs, and containers to different locations by an orchestration function [22].

# 4) MANAGEMENT OF NFs

The NF deployment on a compute node (i.e., physical platform) is typically managed through a logically centralized decision making entity referred to as "Orchestrator". Based on SDN principles, the orchestrator defines and sends orchestration directives to the applications, VMs, and containers to run on compute nodes [11], [23]–[28]. OpenStack [29] and Kubernetes [30], [31] are the mostly commonly adopted dedicated orchestration frameworks in the cloud and data-center management of resources and applications, including VMs and containers. In addition to flexibility, the softwarization

and virtualization of NFs can reduce CAPEX and OPEX of the network operator. In particular, the network operator can upgrade, install, and configure the network with a centralized control entity. Thus, MEC and virtualization are seen as key building blocks of future network infrastructures, while SDN enables efficient network service management.

# B. NEED FOR NF HARDWARE ACCELERATION ON GPC PLATFORM

The NF softwarization makes the overall NF development, deployment, and performance characterization at run time more challenging [11]. Softwarized NFs rely on GPC central processing units (CPUs) to accomplish computations and data movements. For instance, data may need to be moved between input/output (I/O) devices, e.g., Network Interface Cards (NICs), and system memory. However, the GPC platforms, such as the Intel<sup>®</sup> x86-64 [32] and  $AMD^{®}$  [33] CPU platforms, are not natively optimized to run NFs that include routine packet processing procedures across the I/O path [34]-[37]. The shortcomings of GPC platforms for NF packet processing have motivated the development of a variety of software and hardware acceleration approaches, such as the Data Plane Development Kit (DPDK) [38], Field Programmable Gate Array (FPGA), Graphics Processing Unit (GPU), and Application Specific Integrated Circuit (ASIC) [39], to relieve the hardware CPU from computeintensive tasks generated by the NFs, such as data link layer frame switching, IP look-up, and encryption [40].

The deployment of softwarized NFs on GPC platforms achieves a high degree of flexibility. However, it is important to note that critical NF functionalities can be compromised if the hardware and software functional limitations as well as operational characteristics and capabilities are not carefully considered. Generally, the dynamic CPU characteristics can vary over time. For instance, the cache coherency during memory accesses can introduce highly variable (non-deterministic) latencies in NF packet processing [41]. Moreover, the CPU power and thermal characteristics can vary the base operating frequency, introducing variable processing time behaviors [42]-[44]. Therefore, the softwarization of NFs must carefully consider the various performance implications of NF acceleration designs to ensure appropriate performance levels of NFs deployed on hardware-accelerated GPC platforms. These complex NF performance implications of hardware-accelerated GPC platforms and infrastructures motivate the comprehensive survey of this topic area so as to provide a foundation for the further advancement of the technology development and research on hardware-accelerated platforms and infrastructures for NFs.

# C. CONTRIBUTIONS AND ORGANIZATION OF THIS SURVEY

In order to inform the design of hardware acceleration for the processing of softwarized NFs on GPC platforms, this article comprehensively surveys the relevant existing enabling technologies and research studies. Generally, the processing

of a software application task is essentially achieved by a set of hardware interactions. Therefore, understanding hardware features provides a key advantage in the design of software applications. In contrast to a generic software application, an NF involves typically extensive I/O interactions, thus, the NF compute processing largely depends on hardware support to achieve high throughput and short latency for NF packet processing. However, the NF implementation relies not only on I/O interactions for packet transmission and reception, but also requires memory for tunneling and encapsulation, storage for applications (e.g., store-and-forwarding of media), as well as computing (e.g., for cryptography and compression).

This article provides an authoritative up-to-date survey of the hardware-accelerated platforms and infrastructures that speed up the processing of NF applications. The term "platform" as used in this survey article consolidates all the physical hardware components that can be used to build a complete system to support an Operating System (OS) to drive an application. The platform includes the Basic Input Output System (BIOS), CPU, memory, storage, I/O devices, dedicated and custom accelerators, switching fabric, and power management units. The term "infrastructure" corresponds to the end-to-end connectivity of platforms, such as network components, switches, Ethernet, and wireless links. Platform and infrastructure together constitute a complete hardware framework to support an NF.

Despite the wealth of surveys on NFs and their usage in a wide variety of networking contexts, to the best of our knowledge, this present survey article is the first comprehensive survey of hardware-accelerated platform and infrastructure technologies and research studies for the processing of NFs. We give an overview of the related surveys in Section I-D and provide background on the processing of NFs in Section II. Section III comprehensively surveys the relevant enabling technologies for hardware-accelerated platforms and infrastructures for processing NFs, while Section IV comprehensively surveys the related research studies. For the purpose of this survey, we define enabling technologies as designs, methodologies, and strategies that are currently available in the form of a product in the market place; enabling technologies are typically developed by industry or commercially oriented organizations. On the other hand, we define research studies as investigations that are primarily conducted to provide fundamental understanding and insights as well as new approaches and methodologies that aim to advance the overall field; research studies are primarily conducted by academic institutions, such as universities and research labs.

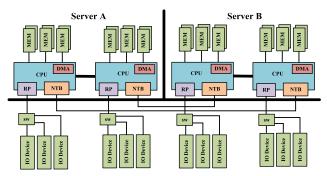

Section III classifies the enabling technologies according to the relevant hardware components that are needed to support the processing of NFs, namely the CPU, interconnects, memory, as well as custom and dedicated accelerators on the platforms; moreover, Section III surveys the relevant infrastructure technologies (SmartNICs and Non-Transparent Bridging). Section IV categorizes the research studies into studies addressing the computer architecture,

interconnects, memory, and accelerators on platforms; moreover, Section IV surveys infrastructure research on Smart-NICs. Section V summarizes the main open challenges for hardware-accelerated platforms and infrastructures for processing softwarized NFs and Section VI concludes this survey article.

#### D. RELATED SURVEYS

This section gives an overview of the existing survey articles on topics related to NFs and their processing and use in communication networks. Sections I-D1 through I-D5 cover topic areas that border on our central topic area, i.e., prior survey articles on topic areas that relate to our topic area in a wider sense. Section I-D6 focuses on prior survey articles that cover aspects of our topic area. Section I-D6 highlights our original survey coverage of hardware-accelerated platforms and infrastructures for NFs with respect to prior related survey articles

# 1) SOFTWARIZATION OF NETWORK FUNCTIONS (NFs)

The NF softwarization can be achieved in different forms, i.e., an NF can be implemented as a software application, as a Virtual Machine (VM), or as a container image. The concept of implementing an NF as a VM has been commonly referred to as Virtualized Network Function (VNF), and Network Function Virtualization (NFV) as a broader term for the technology of implementing, deploying, and managing the VNFs. In general, the NFV concept has been widely discussed in the survey literature [45]-[47]. The traditional challenges of NFV deployment are associated with the virtualization process of NFs, such as overhead, isolation, resource allocation, and function management [48]. Herrera and Botero [49] have discussed the resource allocation and placement of applications, VMs, and containers on GPC platforms. More specifically, Herrera and Botero [49] have surveyed different schemes for the embedding of virtual networks over a substrate network along with the chaining of NFs.

The deployment of an NF as a software application, VM, or container image in the cloud and public networks poses critical security challenges for the overall NFV service delivery. The security aspects and challenges of NFs have been discussed by Yang and Fung [50] and Farris *et al.* [51] for threats against NFs on Internet of Things (IoT) networks; while threat-based analyses and countermeasures for NFV security vulnerabilities have been discussed by Pattaranantakul *et al.* [52]. Furthermore, Lal *et al.* [53] have presented best practices for NFV designs against security threats.

# 2) SOFTWARE DEFINED NETWORKING (SDN) FOR NFs

Software Defined Networking (SDN) provides a centralized framework for managing multiple NFs that are chained together to form a network Service Function Chain (SFC) [54]–[56]. SDN controllers can be used to monitor the resources across multiple platforms to allocate

resources for new SFCs, and to manage the resources during the entire life time of a service. The SDN management strategies for NFs have been summarized by Li and Chen [11]. SDN also provides a platform for the dynamic flow control for traffic steering and the joint optimization of resource allocation and flow control for NFV. The main challenges of SDN-based management is to achieve low control overhead and latency while ensuring the security during the reconfiguration [57]. In contrast to surveys of independent designs of SDN and NFV, Bonfim *et al.* [58] have presented an overview of integrated NFV/SDN architectures, focusing on SDN interfaces and Application Programming Interfaces (APIs) specific to NFV management.

# 3) NETWORK FUNCTION VIRTUALIZATION (NFV) AND NETWORK SLICING

5th Generation (5G) [59]-[61] is a cellular technology that transforms the cellular infrastructure from hardwaredependent deployment to software-based hardwareindependent deployment. 5G is envisioned to reduce cost, lower the access latencies, and significantly improve throughput as compared to its predecessors [62]-[64]. VNFs are an integral part of the 5G infrastructure as NFs that realize the 5G based core network functionalities are implemented as VNFs. In addition to NFV, 5G also adopts SDN for the centralized management of the NFV resources. Yang et al. [65] have presented a survey of SDN management of VNFs for 5G networks, while Nguyen et al. [66] have discussed the relative benefits of different SDN/NFV-based mobile packet core network architectures. Bouras et al. [67] have discussed the challenges that are associated with SDN and NFV based 5G networks, such as scalability and reliability. Costa-Perez et al. [68] have summarized efforts to homogeneously coordinate resource allocation based on SDN and NFV across both fronthaul and backhaul networks in the 5G infrastructure.

In conjunction with SDN and NFV, the technique of network slicing provides a framework for sharing common resources, such as computing hardware, across multiple VNFs while isolating the different network slices from each other. Afolabi et al. [69] have surveyed the softwarization principles and enabling technologies for network slicing. As discussed in the survey by Foukas et al. [70] for VNFs in 5G, for the design of 5G infrastructure, network slicing provides effective management and resource allocation to multiple tenants (e.g., service providers) on the same physical infrastructure. A more general survey on network slicing for wireless networks (not specific to 5G wireless networks) has been presented by Richart et al. [71]. The surveys [72]-[75] have discussed network slicing and the management of resources in the context of 5G based on both SDN and NFV.

# 4) NFV IN MULTI-ACCESS EDGE COMPUTING (MEC)

In contrast to the deployment of VMs and containers in cloud networks, fog and edge networks bring the network services closer to the users, thereby reducing the end-to-end latency. Yi et al. [76] have presented a survey of NFV techniques as applied to edge networks. Some of the NFV aspects that are highlighted by Yi et al. [76] in the context of fog and edge networks include scalability, virtualization overhead, service coordination, energy management, and security. As an extension of fog and edge networks, Multi-Access Edge Computing (MEC) generalizes the compute infrastructure at the edge of the access network. A comprehensive MEC survey has been presented by Tanaka et al. [77], while the role of NFV in MEC has been surveyed by Taleb et al. [78]. The use of both SDN and NFV provides strategies for effective management of MEC resources in edge networks as described by Baktir et al. [79] and Blanco et al. [80].

### 5) NFV ORCHESTRATION

NFV service orchestration involves the management of software applications, VMs, and containers which implement NFs. The NFV management constitutes the storage of VNF images, the allocation of resources, the instantiation of VNFs as runtime applications, the monitoring of the NFV performance, the migration of the VNFs between different hosts, and the shutting down of VNFs at the end of their life time. De Sousa et al. [81] have presented a survey of various methods for managing NFV services. In contrast to NFV management, the orchestration of service function chaining (SFC) adds more complexity since an SFC involves the management of multiple VNFs for a single network service. The SFC complexities, such as compute placement, resource monitoring, and flow switching have been outlined in a survey article by Mechtri et al. [82]. Duan et al. [83] have presented a survey on SDN-based orchestration studies for NFV management.

# 6) ACCELERATION OF NFs

NFs typically require the routine processing of packets involving intense Input/Output (I/O) activities into and out of the compute platform [84]. Since GPC platforms are not fundamentally designed for packet processing, GPC platforms require additional acceleration techniques for effective highspeed packet processing [85]. Linguaglossa et al. [86] have provided a tutorial introduction to the broad NFV field and the overall NFV ecosystem, including tutorial introductions to software acceleration (inclusive of the related ecosystem of software stacks) and hardware acceleration of NFV. The hardware acceleration section in [86] focuses mainly on a tutorial introduction to the general concept of hardware offloading, mainly covering the general concepts of offloading to commodity NICs and SmartNICs; an earlier brief tutorial overview of hardware offloading had appeared in [87]. However, a comprehensive detailed survey of specific hardware offloading technologies and research studies is not provided in [86]. Zhang [88] has presented an overview of NFV platform designs; whereby, Zhang defines the term "NFV platform" to broadly encompass all hardware and software components involved in providing an NFV service (in contrast, we define the term "platform" to only refer to the physical computing entity). Zhang [88] mainly

covers the VNF software and management aspects, i.e., Management and Orchestration (MANO) components [89], that are involved in NFV deployments. Zhang [88] covers hardware acceleration only very briefly, with only about ten references in one paragraph. In contrast to [86] and [88], we provide a comprehensive survey of hardware-accelerated platforms and infrastructures for NF processing. We comprehensively cover the technologies and research studies on the hardware acceleration of CPUs, interconnects, and memory, as well as the accelerator devices on platforms, and furthermore the hardware acceleration of infrastructures (which in our classification encompass SmartNICs) that benefit NF processing.

FPGAs can be programmed with different functions, thereby increasing design flexibility. FPGA-based acceleration in terms of application performance is limited by the transistor-gate density and CPU-to-I/O transactions. Additionally, the FPGA configuration time is relatively longer than initiating the running of a compiled executable on a GPU or CPU. While GPUs are beneficial for running numerous parallel, yet simple computations, the FPGA advantages include the support for complex operations which can be a differentiating factor for compute-intensive workloads [90]. NF applications that require specialized computeintensive functions, such as security, can achieve superior performance with FPGAs as compared to GPUs and CPUs. Niemiec et al. [91] have surveyed FPGA designs for accelerating VNF applications covering the use cases that require compute-intensive functions, such as IPSec, intrusion detection systems, and deep packet inspection [92]. The Niemiec et al. survey [91] includes FPGA internals, virtualization and resource slicing of FPGA, as well as orchestration and management of FPGA resources specifically for NFV deployments. In contrast, our survey includes FPGAs operating in conjunction with CPUs, i.e., FPGAs as platform capability enhancements, to assist in accelerating general NF applications (that are not limited to NFV deployments, but broadly encompass arbitrary NF applications, including e.g., baremetal applications).

### **II. BACKGROUND ON NF IMPLEMENTATION**

In this section we provide background on Network Functions (NFs), discuss various forms of NF implementation, and common acceleration strategies. An NF is a compute operation on a packet of an incoming traffic stream in a compute host. NF examples range, for instance, from a simple IP header look-up for packet forwarding to complex operations involving security negotiations of an end-to-end connection. NFs can also be indirect functions, such as statistical analysis of traffic, network port management, and event monitoring to detect a Denial-of Service (DoS) attack. Traditionally, an NF is implemented with dedicated hardware and software components (see Sec. II-A). Recently, with the softwarization of NFs, the trend is towards implementing NFs as software running on General-Purpose Computing (GPC) platforms. A softwarized NF running on a GPC platform

can be designed as: a bare-metal (BM) implementation on a native OS (as user application) or as a part of the OS (as kernel module) (see Sec. II-B), as application running on an OS, i.e., as user application, or as kernel module as part of the OS (see Sec. II-C), as Virtual Machine (VM) on a hypervisor (see Sec. II-D), or as container running on a container engine (see Sec. II-E). Brief background on general acceleration strategies for NFs running on GPC platforms is given in Sec. II-F.

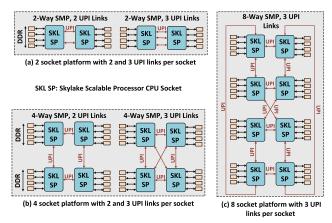

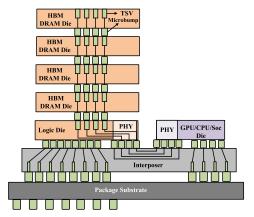

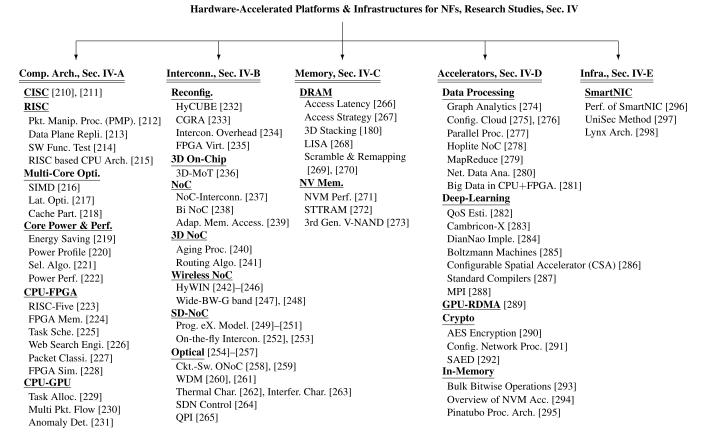

Before we delve into the background on NFs, we give a brief overview of the terminology used for structures on GPC processor chips. The term "package" refers to several hardware components (e.g., CPU, memory, and I/O devices) that are interconnected and packed to form a system that is integrated into a single unit with metallic finishing for physical mounting on a circuit board. That is, a package is a typical off-the-shelf product that is available as a full hardware module and that can be plugged into a server-chassis. A package is often a combination of CPU and non-CPU components, such as memory (DRAM modules), I/O devices, and accelerators. The multiple components in a package are usually interconnected with silicon vias or metallic wires. A GPC platform consists typically of multiple packages.

Typically, a commercially available "chip", such as a processor chip or a RAM chip, is a full System-on-Chip (SoC). A GPC processor chip is typically, in the socket form-factor. We may therefore use the terminology "CPU chip" and "socket" interchangeably; synonymous terminologies are "CPU socket" and "CPU slot". Generally, a package contains only a single CPU socket (plus other non-CPU components). Also, a given CPU socket consists generally of only a single CPU chip. A given CPU chip contains typically a single CPU die, which in turn consists typically of multiple CPU cores. (Possibly, a CPU chip could contain multiple CPU dies that are interconnected with an embedded multi-die interconnect bridge, see Sec. IV.B.) A die is a single silicon entity that is etched in one shot during fabrication.

# A. DEDICATED HARDWARE BASED NF IMPLEMENTATION

### 1) OVERVIEW

The traditional implementation of an NF was through the design of dedicated hardware and software, such as offthe-shelf network switches, routers, and gateways [93]-[95]. Hardware based systems are driven by an embedded software (firmware, microcode), with microprocessor, microcontroller, Digital Signal Processor (DSP), or Application-Specific Integrated Circuit (ASIC) modules. Embedded software for hardware control is generally written in low-level languages, such as C or assembly. The designs are tightly focused on a specific prescribed (dedicated) task. For instance, if the design is to route packets, the embedded hardware and software components are programmed to route the packets. Hence, dedicated hardware NF implementations are fixed implementations that are designed to perform a dedicated task, except for the management configuration of the device and NF.

### 2) BENEFITS

Implementation with dedicated hardware and software achieves the best performance for the dedicated task due to the constrained nature of task processing. As opposed to the processes and task scheduling in an OS, processes running on dedicated hardware use static (fixed) resource allocation, thereby achieving a deterministic packet processing behavior. Dedicated NF hardware units are also energy efficient as no processing cycles are wasted for conversions, e.g., privileges of execution, modes of operation, and address translations, in OSs and hypervisors.

#### 3) SHORTCOMINGS

A main shortcoming of NF hardware implementation is very limited flexibility. Reconfigurations require additional efforts, such as intervention by a network administrator. Moreover, NF hardware (HW) is typically locked into vendors due to proprietary designs, procedures, and protocols. The overall cost of dedicated hardware products could be relatively high since the deployment and maintenance require specialized skills and specialized vendor assistance.

### B. BARE-METAL (BM) NF IMPLEMENTATION

### 1) OVERVIEW

Hardware resources that directly host software tasks, e.g., applications, for computing and I/O without any additional abstraction (except for the OS that directly hosts the software task) are referred to as Bare-Metal (BM) hardware [96]. In contrast to BM hardware, the other forms of hardware include abstracted hardware (i.e., virtualized HW). In theory and practice, there can be multiple layers of abstraction, achieving nested virtualization [97], [98]. Abstraction of hardware resources reduces the complexity of operating and managing the hardware by the application which can help the application to focus on task accomplishment instead of managing the hardware resources. The BM implementation can provide direct access to hardware for configurability, reducing the overheads for computing and for hardware interactions for I/O. The application performance on BM as compared to abstracted hardware, i.e., on a VM or container, has been examined in Yamato [99].

# 2) BENEFITS

The BM implementation of NFs can achieve relatively higher performance as compared to NFs running on virtualized and abstracted environments [99]. The high BM performance is due to the low overhead during NF compute tasks. The instruction and memory address translations required by abstractions are avoided by BM implementations. The BM implementation also provides direct access to OS resources, such as the kernel, for managing the memory allocation, prioritizing the scheduling processing, and controlling I/O transactions.

### 3) SHORTCOMINGS

The BM implementation of an NF does not provide a secure and isolated environment to share the hardware resources with other NFs on the same BM. If multiple NFs run on the same BM hardware, multiple NFs can interfere with each other due to the contention for resources, such as CPU, cache, memory, and I/O resources, resulting in non-deterministic behaviors. Running a low number of NFs to avoid interference among NFs can result in low resource utilization. Hence, the management of applications could incur additional computing as well as a higher management cost. NF implementation on BM with hardware-specific dependencies can result in reduced scalability and flexibility.

# C. APPLICATION AND KERNEL BASED NF IMPLEMENTATION

### 1) OVERVIEW

In general, NFs are mainly deployed as applications which implement the overall packet processing functionality. In contrast to the NF implementation as a user-space application, NF tasks can also be embedded into the kernel as a part of the OS. Generally, there are two types of processes that are run by the OS on the CPU: *i*) applications that use the user-space memory region, and *ii*) more restrictive kernel (software) modules that use the kernel-space memory region. However, a kernel-based NF provides little or no control to the user for management during runtime. Therefore, NFs are mainly run as applications in the user-space execution mode in an OS.

The user-space has limited control over scheduling policies, memory allocation, and I/O device access. However, NFs in the user-space are given special permissions through kernel libraries and can access kernel-space resources (i.e., low-level hardware configurations). Some NF applications, such as authentication, verification, and policy management, may not always require hardware interactions and special kernel-space access. Therefore, the design of NF applications should consider the hardware requirements based on the nature of the task, i.e., whether an NF is time-sensitive (e.g., audio packets), memory intensive (e.g., database management), or compute intensive (e.g., encryption/decryption). Some examples of high-level NF applications with low resource dependencies are data validation, traffic management, and user authentication.

# 2) BENEFITS

Application based NFs have simple development, deployment, and management. Most NFs are designed and deployed as user-space application in an OS. User-space applications generally consume lower compute, memory, and I/O resources compared to abstraction and isolation based implementations, such as container and VMs.

#### 3) SHORTCOMINGS

NF applications that are implemented in the user-space are vulnerable to security attacks due to limited OS protection.

Also, user-space applications are not protected from mutual interference of other NF applications, thus there is no isolation among tasks, resulting in non-deterministic execution of NF tasks. Moreover, user-space applications fall short for networking tasks that require near real-time reaction as the requests propagate through memory regions and follow traditional interrupt mechanisms through I/O hardware.

# D. VIRTUAL MACHINE (VM) BASED NF IMPLEMENTATION

### 1) OVERVIEW

To flexibly manage NFs with effective resource utilization and isolation properties, NFs can be implemented as an application running on a Virtual Machine (VM). A VM is typically implemented as a guest OS over a host OS. The host OS abstracts the hardware resources and presents a virtualized hardware to the guest OS. The software entity (which could be part of the host OS) that abstracts and manages the hardware resources is referred to as a hypervisor. An NF can then be implemented as a kernel module or as a user-space application on the guest OS. A host OS/hypervisor can support multiple guest OSs through sliced resource allocation to each guest OS, thus providing a safe virtual environment for the NF execution.

### 2) BENEFITS

VM based NF implementation provides a high degree of flexibility in terms of deploying and managing the NFs. Multiple instances of the same NF can be instantiated through duplication of VM images for scalability and reliability. VM images can also be transported easily over the network for the instantiation at a remote site. Additionally, multiple NFs can be hosted on the same host OS, increasing the effective resource sharing and utilization. A VM is a complete OS, and all the dependent software necessary for the execution of an NF application is built into the VM, which improves the compatibility across multiple host OSs and hypervisors.

# 3) SHORTCOMINGS

In general, the performance of an NF implemented as a VM is lower than BM and OS based implementation, since virtualization incurs both compute and memory overhead [99]. Since a VM is also a fully functional OS, the overall memory usage and execution processes are complex to design and manage as compared to a user-application based NF running on an OS without virtualization. NF software implementation issues are complex to trace and debug through multiple layers of abstraction. Deployment cost could be higher due to the need for specialized support for the VM management [100].

# E. CONTAINER BASED NF IMPLEMENTATION

# 1) OVERVIEW

The VM based NF implementation creates a large overhead for simple NFs, such as Virtual Private Network (VPN) authentication gateways. Scaling and migrating VMs requires large memory duplications, which result in overall long latencies for creating and transporting multiple VM instances. The concept of workload containerization originated for application management in data centers and the cloud to overcome the disadvantages of VMs [101]. Containers have been designed to create a lightweight alternative to VMs. A key difference between a VM and a container is that a container shares the host OS kernel resources with other containers, while a VM shares the hardware resources and uses an independent guest OS kernel. The sharing of host OS resources among containers is facilitated by a Container Engine (CE), such as Docker. NFs are then implemented as a user-space application running on a container [102]. The primary functions of a CE are:

- *i*) Provides Application Programming Interfaces (APIs) and User Interfaces (UIs) to support interactions between host OS and containers.

- *ii*) Container image management, such as storing and retrieving from a repository.

- *iii*) Configuration to instantiate a container and to schedule a container to run on a host OS.

### 2) BENEFITS

The primary benefits of containerization are the ease of NF scalability and flexibility. Containers are fundamentally designed to reduce the VM management overhead, thus facilitating the creation of multiple container instances and transporting them to different compute nodes. Container based NFs support cloud-native implementation, i.e., to inherently follow the policies applied through a cloud management framework, such as Kubernetes. Containerization creates a platform for NFs to be highly elastic to support scaling based on the demand during run time, resulting in Elastic Network Functions (ENFs) [103].

# 3) SHORTCOMINGS

Critical shortcomings of containerization of an NF are:

- *i*) Containers do not provide the high levels of security and isolation of VMs.

- *ii*) A container can run on BM hardware; whereas, a VM can run both on a hypervisor and on BM hardware.

- *iii*) Only the subset of NF applications that support a modularized software implementation and have low hardware dependencies can be containerized.

- iv) Containers do not provide access to the full OS environment, nor access to a Graphic User Interface (GUI). Containers are limited to a web-based user interface that provides simple hypertext markup language (HTML) rendering for applications that require user interactions, e.g., for visualizations and decisions based on traffic analytics.

### F. ACCELERATION STRATEGIES FOR NF IMPLEMENTATION

NF softwarization should carefully consider different design strategies as one design strategy does not fit all application needs. In addition to the discussed software implementation

designs (Sections II-B– II-E), we need to consider acceleration techniques to facilitate the NF application to achieve optimal performance in terms of overall system throughout, processing latency, resource utilization, energy, and cost, while preserving scalability and flexibility. Towards these goals, acceleration can be provided in either software or hardware.

### 1) SOFTWARE ACCELERATION METHODS

### a: OVERVIEW

Typically, an NF on a GPC infrastructure requires an application running on a traditional OS, such as Linux or Windows, whereby, an application can also be hosted inside a VM or container for abstraction, security, and isolation requirements. However, traditional OSs are not natively designed towards achieving high network performance. For instance, an OS network driver typical operates in interrupt mode. In interrupt mode, a CPU is interrupted only when a packet has arrived at the Network Interface Card (NIC), upon which the network driver process running on the CPU executes a subroutine to process the packet waiting at the NIC. If the CPU is in a power-saving deep sleep state due to inactivity, waking the CPU would take several cycles which severely lengthens the overall packet processing latency. An alternative to the interrupt mode is polling. However, polling of the NIC would significantly reduce the ability of the CPU to perform other tasks. Thus, the interrupt mode incurs relatively long latencies, while keeping the CPU and power utilization low. However, the interrupt mode generally does not maximize the overall throughput (total packets processed by the CPU per second), which requires the batching of packets and is more readily achieved with polling [104].

Some of the examples of software acceleration strategies are:

- i) Polling strategies of I/O devices for offloading task completions and I/O requests.

- *ii*) Continuous memory allocation, and reduction in memory copies between processes and threads.

- iii) Reduced virtual to physical address translations.

- iv) Maintaining cache coherency during memory accesses.

- iv) Scheduling strategies for resource monitoring and allocation.

### b: BENEFITS

One of most prominent benefits of software acceleration is the low cost of adoption in the market, which also reduces the development to deployment cycle time. Software acceleration requires only very small or no modifications of the existing infrastructure. Software optimizations also pave the way to an open source architecture model of software development. The overall development and deployment of software acceleration reduces the complexity and need for sophisticated traditional hardware acceleration designs; and maximizes the performance and utilization of existing hardware infrastructures.

### c: SHORTCOMINGS

Software acceleration may not provide the best possible system throughput as compared to hardware acceleration to fully utilize the system capacity as the software overhead may cause bottlenecks in the system, e.g., for memory and I/O device accesses. Software implementation also increases the overall energy consumption for a given acceleration as the processing is done by the CPU through a generic instruction set. Higher access control (e.g., root privileges) for user-space applications to achieve software acceleration generally does not go well with isolation and has security implications in terms of privacy as multiple applications could interfere with each other [53]. Also, additional layers of software abstractions for acceleration add more latency for the overall task processing as compared to hardware acceleration.

### 2) HARDWARE ACCELERATION METHODS

#### a: OVERVIEW

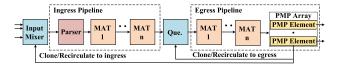

Although software optimizations provide acceleration of NFs, software is fundamentally limited by the CPU availability (i.e., contention with other processes), load (i.e., pending tasks), and utilization (i.e., average idle time) based on the active task computing that the CPU is trying to accomplish. NFs typically require routine tasks, such as IP look-up for network layer (Layer 3) forward routing operations. For data link layer (Layer 2) operations, the MAC look-up and port forwarding that needs to be performed for every frame creates a high I/O bound workload. Similarly, the encapsulation and decapsulation of every packet needed for tunnel-based forwarding constitutes a high memory bound workload. A more CPU intensive type of task is, for instance, encryption and decryption of IP packets for security. In order to maximize the performance, the CPU has to frequently monitor the NIC and has to process the IP packets as part of an NF; both of these actions consume large numbers of CPU cycles. Therefore, hardware based acceleration is critical for NF development and deployments.

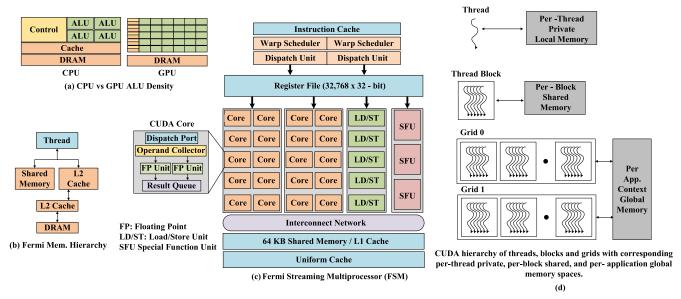

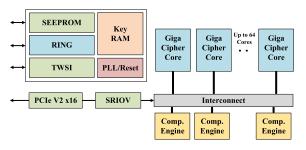

Hardware acceleration can be broadly categorized into custom acceleration and dedicated acceleration. Custom acceleration is generic and programmable according to the application requirements either at run-time or preloaded based on the need. Examples of custom acceleration are Graphic Processing Unit (GPU) and Field Programmable Gate Arrays (FPGA). In contrast, dedicated hardware acceleration is designed and validated in hardware for a defined function, with little or no programming flexibility to change the behavior of the hardware at run-time. On the other hand, custom hardware acceleration is cost effective and easy to configure which helps in developing new protocols and behaviors that are adapted to the applications.

# b: BENEFITS

As compared to software acceleration, hardware acceleration provides more robust advantages in terms of saving CPU cycles that execute the NF processing tasks than

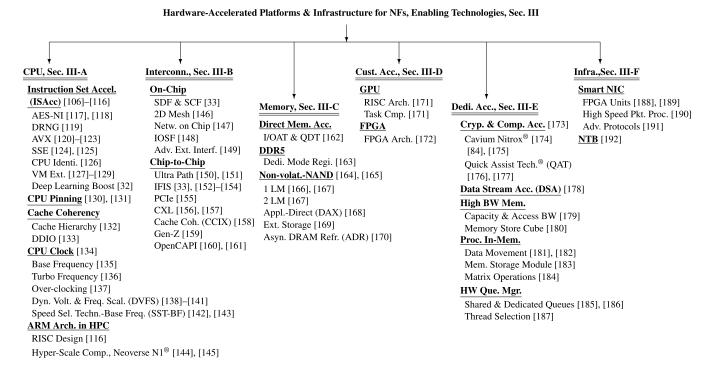

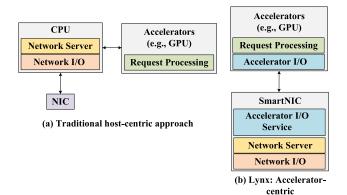

FIGURE 2. Classification taxonomy of enabling technologies for hardware-accelerated platforms and infrastructures for processing softwarized NFs: The main platform related categories are hardware accelerations for the CPU, interconnects, and memory, as well as custom and dedicated hardware accelerators that are embedded on the platform; the infrastructure hardware accelerations focus on network interface cards and bridging.

implementation as a software. Overall, hardware accelerators significantly improve the system throughput and task latency as well as energy efficiency for NF implementations [105].

### c: SHORTCOMINGS

The main shortcomings of hardware accelerations are:

- *i*) Longer time frame for development cycle than for software acceleration development.

- ii) For every hardware component there is an associated software component that needs to be developed and maintained.

- *iii*) Introduction of new technologies, newer specifications and skills to manage the hardware.

- iv) Higher cost of implementation and adoption into market.

- v) Infrastructure upgrades with new hardware components are difficult

- vi) Locked-in vendors for hardware and maintenance support.

# III. ENABLING TECHNOLOGIES FOR HARDWARE-ACCELERATED PLATFORMS AND INFRASTRUCTURES FOR NF IMPLEMENTATION

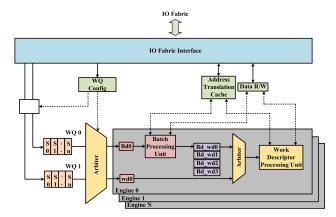

This section comprehensively surveys the enabling technologies for hardware-accelerated platforms and infrastructures for implementing NFs. This section is structured according to the classification structure of the enabling technologies in Fig. 2, whereby a subsection is dedicated to each of the main categories of enabling technologies, i.e., CPU, interconnects, memory, custom accelerators, dedicated accelerators, and infrastructure.

#### A. CENTRAL PROCESSING UNIT (CPU)

Traditionally in the current deployments, the CPU performs nearly all the computing required by an NF. While most NF computing needs can be met by a CPU, an important question is to decide whether a CPU is the ideal resource to perform the NF tasks. For instance, a polling function only continuously monitors a hardware register or a memory location; a CPU may not be well suited for such a polling function. This section comprehensively surveys the enabling technologies for accelerating the operation of the CPU hardware for processing NFs.

### 1) INSTRUCTION SET ACCELERATION (ISAcc)

An instruction is a fundamental element that defines a CPU action. A CPU action can be a basic operation to perform an arithmetic or logic operation on two variables, to store or to retrieve data from memory, or to communicate with an external I/O device. The instruction set (IS) is a set of instructions that are pre-defined; the IS comprehensively lists all the CPU operations. In the computing literature, the IS is also commonly referred to as Instruction Set Architecture (ISA); for brevity, we use the terminology "Instruction Set (IS)" and define the acronym "ISAcc" to mean "Instruction Set Acceleration". The properties of the IS list distinguish the type of CPU, typically as either Reduced Instruction Set Compute (RISC) or Complex Instruction Set Compute (CISC) [106]. Generally, RISC has a very basic set of limited operations, while CISC includes a comprehensive set of instructions targeted at complex operations. RISC is

TABLE 1. CPU Instruction Set Acceleration (CPU-ISAcc) extensions: AES-NI, DRNG, and AVX-512. CPU-ISAcc optimizes hardware implementations of software functions, such as random number generation, cryptographic algorithms, and machine learning, in terms of power and performance.

|         | CPU Instruction | Acceleration Function       |  |

|---------|-----------------|-----------------------------|--|

|         | AESENC          | One round AES encryp. flow  |  |

|         | AESNCLAST       | Last round AES encryp. flow |  |

|         | AESDEC          | One round AES decryp. flow  |  |

| AES-NI  | AESDECLAST      | Last round AES decryp. flow |  |

|         | AESKEYGENASSIST | AES round key generation    |  |

|         | AESIMC          | AES Inverse Mix Columns     |  |

|         | PCLMLUQDQ       | Carryless multiply          |  |

| DRNG    | RDRAND          | Hardwgen. random value      |  |

| DKNG    | RDSEED          | Hardwgen. random seed value |  |

|         | VNNI            | Vector Neural Net. Instr.   |  |

| AVX-512 | GFNI            | Galois Field New Instr.     |  |

|         | VAES            | Vector AES Instructions     |  |

|         | VBMI2           | Vector Byte Manip. Instr. 2 |  |

|         | BITALG          | Bit Algorithms              |  |

power and silicon-space efficient. However, the limited set of RISC operations generates large amounts of translated machine opcodes from a high-level programming language which will reduce performance for complex operations, such as encryption or compression. On the other hand, CISC can implement a complex operation in a single CPU *instruction* which can result is smaller machine opcodes, improving the performance for complex operations. However, CISC generally consumes higher power and requires more silicon-space than RISC.

Tensilica [107] is an example of a low-power DSP processor based on the RISC architecture which is optimized for floating point operations [108]. Tensilica processors are typically used in the design of I/O devices (e.g., NIC) and hardware accelerators in the form of new IS definitions and concurrent thread execution to implement softwarized NFs. The IS extensions have been utilized to accelerate hashing NFs [109], [110] and dynamic task scheduling [111]. Similar IS extensions have accelerated the complex network coding function [112], [113], [193] in a hardware design [114].

ISAcc [115], [116] provides an additional set of instructions for RISC and CISC architectures. These additional instructions enable a single CPU *instruction* to perform a specific part of the computation that is needed by an application in a single CPU execution cycle. The most important CPU instructions that directly benefit NF designs are:

# a: ADVANCED ENCRYPTION STANDARD-NEW INSTRUCTIONS (AES-NI)

Advanced Encryption Standard-New Instructions (AES-NI) [117], [118], see Table 1, include IS extensions to compute the cryptography functions of the Advance Encryption Standard (AES); in particular, AES-NI includes the complete encryption and decryption flow for AES, such as AES-GCM (AES-GCM is a type of AES algorithm, and AES-ENC is used internally for GCM encryption). AES-NI has been widely used for securing HTTPS connections needed for end-to-end NFV instances over networks. HTTP uses the Transport

Layer Security (TLS) Secure Sockets Layer (SSL) protocol (which incorporates AES) to generate and exchange keys as well as to perform encryption and decryption. SSL implementations, such as OpenSSL, provide the interface and drivers to interact with the AES-NI CPU acceleration instructions.

### b: DIGITAL RANDOM NUMBER GENERATOR (DRNG)

The Digital Random Number Generator (DRNG) [119] with the RDRAND instruction can be used for generating public and private cryptographic keys. The RSEED instruction can be used for seeding software-based Pseudorandom Number Generators (PRNGs) used in cryptography protocols. DRNG is also extensively used in modeling, analytics for random selections, large scale system modeling to introduce randomization, natural disturbances, and noises in encryption and control loop frameworks, which are applicable to SDN controller-based NF designs.

### c: ADVANCED VECTOR EXTENSIONS (AVX)

The Advanced Vector Extensions (AVX) [120], [121], see Table 1, implement an advanced data processing IS for machine learning, encryption, and signal processing [122]. The vectorization of the CPU processing significantly improves the data computations for large vector data sets [123].

### d: STREAMING SIMD EXTENSIONS (SSE)

The Streaming SIMD Extensions (SSE) [124], [125] implement accelerations aimed at string and text character processing, which is essential for searches and comparisons. NFs rely on JavaScript Object Notation (JSON), extensible markup language (XML), and text parsing protocols to perform management functions. SSE instructions play an important role in achieving near-real-time decisions based on text look-up and comparisons. SSE instructions also implement compute functions for 32 bit Cyclic Redundancy Checks (CRC32) which are commonly used in data transfer and external storage NFs.

### e: CPU IDentification (CPUID)

The CPU IDentification (CPUID) [126] instruction provides the details of CPU specifications, enabling software to make decisions based on the hardware capabilities. A user can write a predefined value to the EAX CPU register with the CPUID instruction to retrieve the processor specific information that is mapped to the value indicated by the EAX CPU register. A comprehensive list of CPU specifications can be enumerated by writing values in sequence to the EAX and reading the EAX (read back the same write register), as well as the related EBX, ECX, and EDX CPU registers. For instance, writing 0x00h to the EAX provides the CPU vendor name, whereas writing 0x07h gives information about the AVX-512 IS capability of the CPU. NF orchestration can use the CPUID instruction to identify the CPU specifications along with the ISAcc capabilities to decide whether an NF can be run on the CPU or not.

# f: VIRTUAL MACHINE EXTENSIONS (VMX)

The Virtual Machine Extensions (VMX) [127]-[129] provide advanced CPU support for the virtualization of the CPU, i.e., the support for virtual CPUs (vCPUs) that can be assigned to VMs running on a Virtual Machine Monitor (VMM) [194], [195]. In the virtualization process, the VMM is the host OS which has direct controlled access to the hardware. VMX identifies an instruction as either a VMX root operation or a VMX non-root operation. Based on the instruction type provided by the VMX, the CPU executes a VMX root operation with direct hardware access, while a VMX non-root operation is executed without direct hardware access. The two most important aspects in virtualization are: a) VM entries, which correspond to VMX transitions from root to non-root operation, and b) VM exits, which correspond to VMX transitions from non-root to root operation. NFs implemented on a virtual platform should be aware of the VMX principles and whether an NF requires root operations to take the advantage of performance benefits in root-based operations.

# q: DEEP LEARNING (DL) BOOST

The Deep Learning (DL) Boost IS acceleration on Intel® CPUs [32] targets machine learning and neural network computations. The traditional implementation of floating point operations results in extensive Arithmetic and Logic Unit (ALU) computations along with frequent accesses to registers, caches, and memory. DL Boost transforms floating point operations to integer operations, which effectively translates the higher precision floating point multiply and addition operations to lower precision integer calculations. The downside is the loss of computation accuracy. However, for machine learning and neural network computations, a loss of accuracy is often tolerable. DL Boost can transform Floating Point 32 bit (FP32) operations to FP16, INT8, and further down to INT2. DL boost reduces the multiply-and-add operations, which increases system throughput while reducing latency and power consumption. An NF that requires low precision floating operation for prediction, estimation, and machine learning applications can benefit from DL Boot acceleration of the CPU IS.

# 2) CPU PINNING

CPU pinning is a resource allocation strategy that allocates and pins a specific workload to a specific physical CPU core. Traditionally, in the OS, application threads and processes are dynamically scheduled on the CPU cores based on their relative priorities and processing states, such as wait and ready-to-run. As opposed to the OS management of CPU resources, the dedicated and static allocation of CPU core resources for the execution of application threads and processes improves the performance of the pinned application [130], [131]. In addition to no-contention of resources, the performance benefits of CPU pinning are attributed to the data cache coherency, especially at the L1 and L2 cache levels

(which reside within the CPU core), when only one application accesses a memory location from a given CPU core.

In virtualization, the VMM scheduler allocates the CPU resources to VMs, i.e., the conversion of instructions to a virtual CPU (vCPU) to an actual physical CPU (pCPU) is achieved dynamically at run time. However, the VMM scheduler may impact the overall performance when there is resource contention by other VMs running on a VMM; in addition, VM based cache coherency issues may arise. Therefore, CPU pinning is an important aspect to consider for the CPU resource allocation (vCPU or pCPU) to a virtualized NF (VNF) via CPU pinning.

# 3) CACHE COHERENCY

Caches play an important role in the overall software execution performance by directly impacting the latency of memory accesses by the CPU. The memory access flow from a CPU first performs an address translation from a virtual address to a physical address. If the address translation fails, then a page fault is registered and a page walk process is invoked. If the address translation succeeds, then cache levels are checked. If there is a cache hit, then the data is read from or written to the cache; whereas, if there is a cache miss, then an external memory read or write is performed. A cache miss or an address translation failure page walk significantly increase the latency and severely impede the NF performance. Therefore, NF designs have to carefully consider the cache coherency of data accesses.

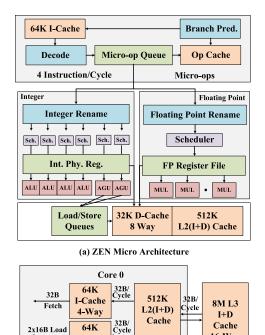

#### a: CACHE HIERARCHY

The cache hierarchy has been commonly organized as follows:

- i) The level L1 cache for code is normally closest to the CPU with the lowest latency for any memory access. A typical L1 cache for code has a size of around 64 kilobytes (KB), is shared between two cores, and has 2-way access freedom. The L1 cache for code is commonly used to store opcodes in the execution flow, whereby a block of opcodes inside a loop can greatly benefit from caching.

- ii) The level L1 cache for data is a per-core cache which resides on the CPU itself. The L1 data cache typically stores the data used in the execution flow with the shortest access latency on the order of around 3–4 clock cycles.

- *iii*) A typical level L2 cache is shared between two cores and has a size of around 1–2 MB. The access latency is typically around 21 clocks with 1 read for 4 clock cycles and 1 write for 12 clock cycles.

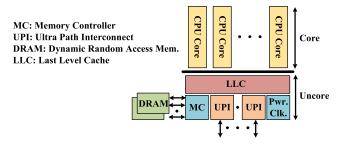

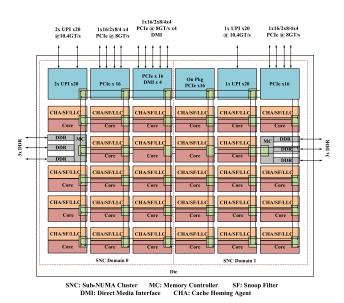

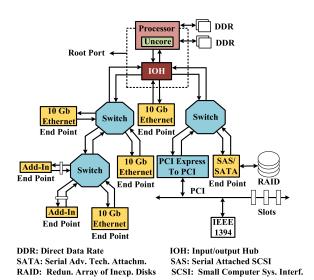

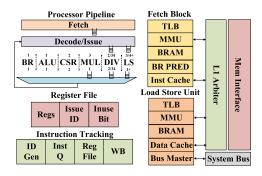

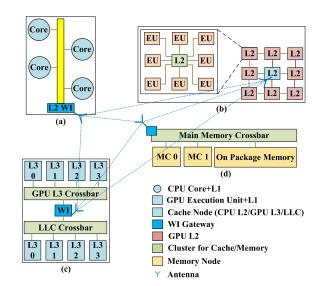

- iv) The level L3 cache is generally referred to as shared Last Level Cache (LLC), which is shared across all cores. The L3 cache is typically outside the CPU die, but may still reside inside the processor die. A typical processor die consists of core and uncore elements [132] (see Fig. 3). Uncore elements refer to all the non-CPU

FIGURE 3. Components inside processor chips are generally functionally separated into core (i.e., CPUs) and uncore elements. Uncore elements are non-core components, such as clock, memory controllers, integrated accelerators, interrupt controllers, and interconnects.

components in the processor die, such as clock, Platform Controller Hub (PCH), Peripheral Component Interconnect express (PCIe) root complex, L3 cache, and accelerators.

### b: DATA-DIRECT IO (DDIO)

The Data-Direct IO (DDIO) [133] is a cache access advancement I/O technology. The DDIO allows I/O devices, such as the PCIe based NIC, GPU, and FPGA, to directly read and write to the L3 shared LLC cache, which significantly reduces the latency to access the data received from and sent to I/O devices. Traditionally, I/O devices would write to an external memory location which would then be accessed by the CPU through a virtual to physical address translation and a page look-up process. NF applications require frequent I/O transactions, especially to read and write packets between NIC and processor memory. With DDIO, when a packet arrives at the NIC, the NIC directly writes to the cache location that is indexed by the physical address of the memory location in the shared L3 cache. When the CPU requests data from the memory location (which will be a virtual address for CPU requests), the address is translated from virtual to physical, and the physical address is looked up in the cache, where the CPU finds the NIC packet data. The DIDO avoids the page walk and memory access for this packet read operation. A CPU write to the NIC for a packet transmission executes the same steps in reverse. Thus, NF implementations with intense I/O can greatly benefit from the DDIO cache management.

### 4) CPU CLOCK

One of the critical aspects of an NF is to ensure adequate performance when running on a GPC platform. In addition to many factors, such as the transistor density, memory access speeds, and CPU processing pipeline, the CPU operational clock frequency is a major factor that governs the CPU throughput in terms of operations per second. However, in a GPC platform, the CPU clock frequency is typically dynamically scaled to manage the thermal characteristics of the CPU die [134]. The CPU clock frequency directly impacts the total power dissipated as heat on the CPU die.

### a: BASE FREQUENCY

The base frequency [135] is the normal CPU operational frequency suggested by the manufacturer to guarantee the CPU performance characteristics in terms of number of operations per second, memory access latency, cache and memory read and write performance, as well as I/O behaviors. The base frequency is suggested to achieve consistent performance with a nominal power dissipation to ensure sustainable and tolerable thermal features of the CPU die.

### b: TURBO FREQUENCY

The turbo frequency technique [136] automatically increases the platform and CPU operational frequency above the base frequency but below a predefined maximum turbo frequency. This frequency increase is done opportunistically when other CPUs in a multi-core system are not active or operating at lower frequencies. The turbo frequency is set according to the total number of cores running on a given CPU die, whereby the thermal characteristic of the CPU die is determined by the aggregated power dissipated across all the cores on the CPU die. If only a subset of the cores on the CPU die are active, then there is an extra thermal budget to increase the operational frequency while still meeting the maximum thermal limits. Thus, the turbo frequency technique exploits opportunities for automatically increasing the CPU core frequencies for achieving higher performance of applications running on turbo frequency cores.

# c: OVER-CLOCKING

Over-clocking [137] manually increases the CPU clock frequency above and beyond the manufacturer's suggested maximum attainable frequency, which is typically, higher than the maximum turbo frequency. Over-clocking changes the multipliers of the fundamental CPU clock frequency. A clock multiplier on the uncore part of the CPU die generally converts the lower fundamental frequency into the operating base and turbo frequencies. Over-clocking manually alters the multipliers of the clock frequency to reach the limits of thermal stability with an external cooling infrastructure. The thermal budget of the CPU die is forcefully maintained through a specialized external cooling infrastructure (e.g., circulating liquid nitrogen) that constantly cools the CPU die to prevent physical CPU damage from overheating. The highest CPU performance can be achieved through successful over-clocking procedures; however, the cost and maintenance of the cooling infrastructure limit sustained over-clocked operations. Hence only few applications can economically employ over-clocking on a consistent basis.

# d: DYNAMIC VOLTAGE AND FREQUENCY SCALING (DVFS)

Dynamic Voltage and Frequency Scaling (DVFS) [138]–[140] defines a system and a set of procedures that control the operational frequency and voltage in a CPU subsystem. Typically, CPU manufacturers provide several

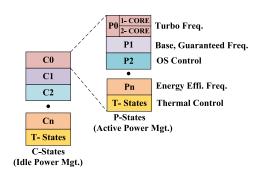

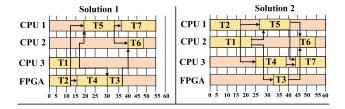

FIGURE 4. Processor states are broadly classified as CPU states (C-States) which indicate the overall CPU state; additionally, when the CPU is active (i.e., in C0), then core-specific Power states (P-States) indicate the operational frequencies of the cores that are actively executing instructions.

operational states (see Fig. 4) including: C0: CPU is actively executing instructions; C1: CPU in halt state with no instruction execution, capable of instantaneously transitioning into C0 state; C2: Stop-Clock, transition to C1 and C0 takes longer; C3: C3 and higher CPU states can be defined as sleep states without power.

In addition to the *C* states, which define the CPU power characteristics, *P* states define the performance characteristics of the individual CPU cores, typically when the CPU is in *C*0. The *P* states include: *P*0: CPU core is operating in turbo frequency mode, the highest performance can be achieved by a specific core; *P*1: CPU core is operating at a guaranteed (base) frequency, a sustained performance can be achieved by all cores; *P*2: CPU core is operating in OS managed lower frequency and voltage, i.e., in low performance modes for *P*2 and subsequent *P* states; *T*: Thermal control is applied to the CPU cores, as the CPU die has reached the limits of the safe operating temperature.

The transitions between different *C* states and *P* states are managed by the DVFS subsystem. The DVFS, in conjunction with the OS and BIOS through the Advanced Configuration and Power Interface (ACPI) [141], tries to attain the best performance for the lowest possible power consumption.

# e: SPEED SELECT TECHNOLOGY-BASE FREQUENCY (SST-BF)

The Intel® Speed Select Technology-Base Frequency (SST-BF) [142] enhances the application performance by increasing the base frequency of the CPU. SST-BF increases the base frequency on demand so as to adaptively boost the application performance. SST-BF is thus particularly well suited for NF acceleration, e.g., for quickly handling bursty network traffic through increasing the base frequency when a traffic burst occurs. In contrast to the turbo frequency technique (see Section III-A4.b), which increases the CPU frequency opportunistically, SST-BF increases the CPU frequency deterministically when there is a need. An NF running on a GPC platform is susceptible to variations of the CPU clock frequency; thus, running an NF application with the opportunistic turbo frequency technique cannot guarantee the Quality-of-Service (QoS) for the NF. Most NFV deployments

require prescribed worst case performance guarantees in order to deliver the services to the users [143]. A high deterministic CPU clock frequency as achieved by SST-BF is an important factor to guarantee the QoS performance.

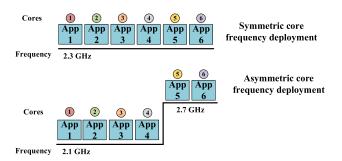

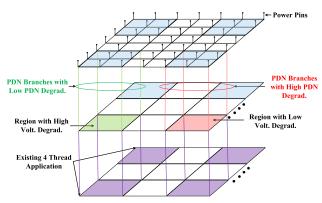

SST-BF segregates the CPU cores into SST-BF supported and non-supported cores based on their relative distance in terms of their thermal characteristics. A system configuration during the start-up enables SST-BF on the supported cores. When the application requests an increased base frequency, the OS sends a configuration command to the supported cores to increase their base frequency (could be maximum supported value as suggested by the manufacturer). At the same time, the operating frequencies of the SST-BF nonsupported CPU cores are reduced so as to maintain the overall average frequency of the cores and to keep the thermal budget of the CPU die within the safe operational range. For instance, if there are 6 cores in a CPU die operating with a normal base frequency of 2.3 GHz (see Fig. 5), and 2 of the SST-BF supported cores request an increased base frequency, the operational frequencies for these two cores would be changed to the maximum base frequency, e.g., 2.7 GHz, while reducing the operational frequencies of the other 4 cores to 2.1 GHz. The OS and the orchestrator can decide which applications to run on the SST-BF supported cores and when to switch the operational frequencies to the supported maximum base frequency on the supported cores.

FIGURE 5. The Intel® Speed Select Technology-Base Frequency (SST-BF) technology [142] deterministically modifies the operating base frequency on specific cores to increase or decrease the base frequencies of the cores at run-time based on the need to provide adequate performance to NF applications running on the cores. In the depicted example scenario, the operating base frequency of two cores is increased to 2.7 GHz while four cores slowed down to 2.1 GHz such that the average operating base frequency across all six cores remains around 2.3 GHz.

# 5) ARM ARCHITECTURES IN HIGH PERFORMANCE COMPUTING (HPC)

RISC and CISC compute architectures with ISAcc support have recently been merging their boundaries to achieve the benefits from both architectures. The demand for low power consumption while achieving high performance has prompted RISC architectures to support High Performance Computing (HPC) capabilities. For instance, the ARMv7 RISC architecture contains the THUMB2 extensions for 16-bit instructions similar to CISC, and the x86 ISAcc performs micro-operation translations that are similar to RISC.

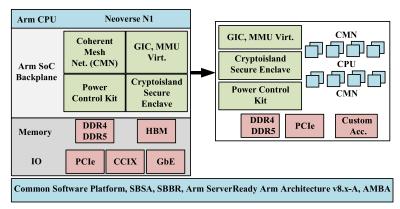

(a) ARM Neoversa N1 CPU

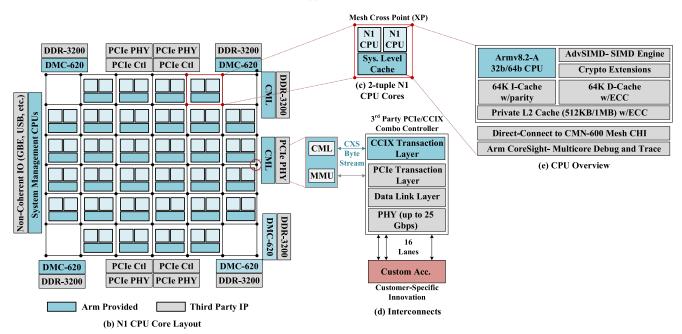

FIGURE 6. Overview of ARM® Nervosa N1 architecture [144]: (a) Illustration of ARM CPU functional blocks along with CPU interconnect, Memory Management Unit (MMU), power management, and security components in relation to third-party memory and I/O components. Nervosa N1 can be extended to server-scale deployments with specifications of Server Base System Architecture (SBSA), Server Base Boot Requirements (SBBR), and Advanced Microcontroller Bus Architecture (AMBA) [149]. ARM Neoverse N1 CPU sits on the ARM SoC backplane (uncore) along with Coherent Mesh Network (CMN) and power control kit. Memory and I/O are third-party modules that interface with ARM designs through interfaces (green and blue blocks are from ARM, while brown and gray color blocks are third-party blocks). The left part of (a) shows the general template arranged as layers of components, such as backplane, ARM CPUs, memory, and I/O devices; while the right part shows the actual scalable view, with a flexibly scalable number of CPUs on top of the CMN, supported by common functional blocks, such as virtualization, security, and power control. (b) Layout overview of N1 CPU cores supported by CMN, with extensions to memory controller and PCIe controllers for external memory and I/O device interfaces. (c) Two-tuple N1 CPU cores and system level cache surrounded by Mesh Cross Points (XPs). (d) Hardware interconnect and interface extensions along with PCIe protocol operations to connect external hardware accelerators with N1 CPUs. (e) Overview of N1 CPU with 64 KB L1 data and instruction cache, 512 KB/1 MB private L2 cache, mesh connect, and debug-and-trace components.

Yokoyama *et al.* [116] have surveyed the state-of-the-art RISC processor designs for HPC computing and compared the performance and power consumption characteristics of the ARMv7 based server platforms to the Intel server platforms. The results from over 400 workload executions indicate that the state-of-the-art ARMv7 platform is 2.3-fold slower than the Sandy Bridge (Intel), 3.4-fold slower than Haswell (Intel), and nearly 7% faster than Atom (Intel). However, the Sandy Bridge (Intel) platform consumes 1.2-fold more power than the ARMv7.

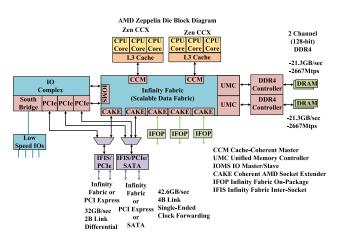

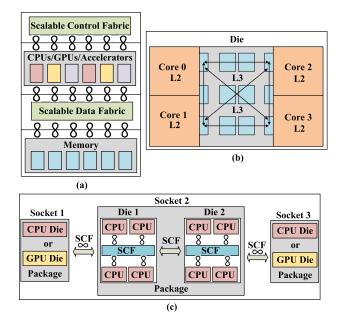

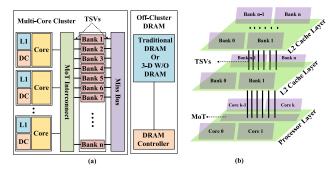

Figure 6 presents an overview of the Neoverse N1 [144] CPU architecture targeted for edge and cloud infrastructures to support hyper-scale computing. The N1 platform can scale from 8 to 16 cores per chip for low computing needs, such as networking, storage, security, and edge compute nodes, whereas, for server platforms the architecture supports more than 120 cores. For instance, a socket form factor of N1 consists of 128 cores on an 8×8 mesh fabric. The chip-to-chip connectivity (e.g., between CPU and accelerator) is enabled by the CCIX® (see Sec. III-B2.e) through a Coherent Mesh

Network (CMN) interfacing with the CPU. The latency over the CMN is around 1 clock cycle per Mesh Cross Point (XP) hop. The N1 supports 8 DDR channels, up to 4 CCIX links, 128 MB of L3 cache, 1 MB of private cache along with 64 KB I-cache and 64 KB D-cache. The performance improvements of N1 as compared to the predecessor Cortex-A72 are: 2.4-folds for memory allocation, 5-folds of object/array initializations, and 20-folds for VM initiation. The Neoverse N1 has been commercially deployed on Amazon Graviton [145] servers, where the workload performance per-vCPU shows an improvement of 24% for HTTPS load balancing with NGNIX and 26% for X.264 video encoding as compared to the predecessor M5 server platforms of Amazon Graviton.

# 6) SUMMARY OF CPU

In summary, the CPU provides a variety of options to control and enable the features and technologies that specifically enhance the CPU performance for NF applications deployed on GPC platforms. In addition to the OS and hypervisors managing the CPU resources, the NF application designers can become aware of the CPU capabilities through the CPU instruction CPUID and develop strategies to run the NF application processes and threads on the CPU cores at desired frequency and power levels to achieve the performance requirements of the NF applications. In general, a platform consists of both CISC and RISC computing architectures, whereby CISC architectures (e.g., x86 and AMD) are predominantly used in hyper-scale computing operations, such as server processors, and RISC architectures are used for compute operations on I/O devices and hardware accelerators.