# GaN Vertical-Channel Junction Field-Effect Transistors With Regrown p-GaN by MOCVD

Chen Yang<sup>®</sup>, Houqiang Fu<sup>®</sup>, Viswanathan Naveen Kumar<sup>®</sup>, Kai Fu<sup>®</sup>, Hanxiao Liu, Xuangi Huang<sup>®</sup> Tsung-Han Yang<sup>®</sup>, Hong Chen, Jingan Zhou<sup>®</sup>, Xuguang Deng, Jossue Montes, Fernando A. Ponce<sup>®</sup>, Dragica Vasileska<sup>®</sup>, *Fellow*, *IEEE*, and Yuji Zhao, *Member*, *IEEE*

Abstract—We report an experimental demonstration of GaN-based vertical-channel junction field-effect transistors (VC-JFETs). A p-GaN regrowth by metalorganic chemical vapor deposition (MOCVD) and a subsequent selfplanarization process were developed to fabricate the GaN VC-JFETs. Fin-like channel regions were patterned by electron beam lithography (EBL) and aligned to *m*-plane or a-plane. The electrical properties of lateral and vertical p-n junctions were characterized to verify the effectiveness of the p-GaN regrowth. Both VC-JFETs with m-plane and a-plane channels show decent gate modulation. We further discussed important factors that may affect the device performance including interfacial impurities and nonuniform acceptor distribution. This work highlights the successful demonstration of GaN VC-JFETs and lateral p-n junctions by an etch-then-regrow process, providing valuable information and reference for the further development of GaN power electronics.

Index Terms-Gallium nitride, junction field-effect transistor (JFET), p-GaN regrowth, selective area doping.

#### I. INTRODUCTION

THE III-nitride semiconductors have attracted consider-L able attention for various applications in optoelectronics [1], [2], photonics [3], [4], and electronics [5]. Recently, GaN-based power electronics have been extensively researched due to GaN's large bandgap  $(E_g)$ , high breakdown electric field  $(E_b)$ , and large Baliga's figure of merit (BFOM). With the commercialization of high-quality bulk GaN substrates, GaN vertical devices have become prominent candidates for the next-generation efficient power electronics, capable of achieving high currents and high breakdown voltages (BVs) with smaller chip area and better thermal management [6]–[8].

Manuscript received March 6, 2020; revised April 21, 2020, May 27, 2020, and July 14, 2020; accepted July 15, 2020. Date of publication August 5, 2020; date of current version September 22, 2020. This work was supported in part by the ARPA-E PNDIODES Program monitored by Dr. Isik Kizilyalli under Grant DE-AR0000868, in part by the NASA HOT-Tech Program under Grant 80NSSC17K0768, and in part by NanoFab through the NSF under Contract ECCS-1542160. The review of this article was arranged by Editor Y. Cao. (Corresponding author: Yuji Zhao.)

Chen Yang, Houqiang Fu, Viswanathan Naveen Kumar, Kai Fu, Xuanqi Huang, Tsung-Han Yang, Hong Chen, Jingan Zhou, Xuguang Deng, Jossue Montes, Dragica Vasileska, and Yuji Zhao are with the School of Electrical, Computer, and Energy Engineering, Arizona State University, Tempe, AZ 85287 USA (e-mail: cyang130@asu.edu; yuji.zhao@asu.edu).

Hanxiao Liu and Fernando A. Ponce are with the Department of Physics, Arizona State University, Tempe, AZ 85287 USA.

Color versions of one or more of the figures in this article are available online at http://ieeexplore.ieee.org

Digital Object Identifier 10.1109/TED.2020.3010183

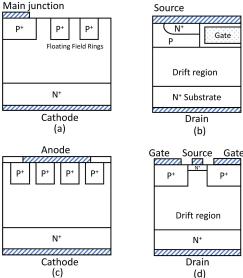

Source Anode Gate Gate P⁺ P P Þ P Drift region N+ N<sup>+</sup> Cathode Drain (c) (d) Schematics of advanced GaN power devices and structures

Fig. 1. enabled by selective area doping. (a) JTE. (b) U-MOSFETs. (c) JBS diodes. (d) JFETs.

However, selective area doping still remains one of the most critical hurdles for GaN power electronics [9]-[12], which hinders the demonstration of many advanced GaN power devices and structures, such as junction termination extension (JTE), U-shape metal-oxide-semiconductor field-effect transistors (U-MOSFETs), junction barrier Schottky (JBS) diodes, and junction field-effect transistors (JFETs) (see Fig. 1). Compared with the immature ion implantation and thermal diffusion methods, etch-then-regrow is still regarded as one of the most promising methods to realize selective area doping in GaN [13]-[16]. Currently, there are still some challenges in etch-then-regrow progress. In an etched trench, the regrowth interfaces are composed of both polar *c*-plane and nonpolar planes (a- or m-plane) that have very different atom arrangements and dangling bond densities, resulting in anisotropic material and electrical properties. For example, the nonpolar planes are more susceptible to contamination and impurity incorporation than the *c*-plane (Ga-face) due to the presence of nitrogen atoms [17]. Another challenge is the nonuniform Mg or acceptor distribution in the trench regrowth. Liu et al. [18] reported that the sidewall of Mg-doped p-GaN grown over a mesa structure was acceptor-deficient, which led to lower hole concentrations on nonpolar sidewall facets.

0018-9383 © 2020 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

Furthermore, the use of common dielectric growth masks, such as  $SiO_2$  and  $Si_3N_4$ , during regrowth can result in Si diffusion into p-GaN, giving rise to n-type conductivity instead of p-type. In this work, the etch-then-regrow utilizes a maskless blanket regrowth process to ensure the regrown p-GaN has p-type conductivity. Although some regrown GaN p-n diodes have been demonstrated by blanket regrowth on planar surfaces [19], the reports on GaN-regrown devices in trenches or fins, such as GaN JFETs, are still scarce.

Recently, the FinFET concept has enlightened vertical power transistors based on wide bandgap (WBG) and ultrawide-bandgap (UWBG) semiconductors [20]. Two types of enhancement-mode vertical GaN field-effect transistors with fin-like channels have been proposed: Fin MOSFETs and vertical-channel junction field-effect transistors (VC-JFETs). Fin MOSFETs use MOS gates to pinch off the fin channel, whereas VC-JFETs rely on lateral p-n junction gates to modulate the fin channel. Both types of devices have the potential to realize kilovolts BVs [21]. In addition, lateral p-n junctions are also building blocks for more complicated bipolar GaN power devices [7]. Sun et al. [22] demonstrated GaN Fin MOSFETs with a threshold voltage of 1 V and specific ON-resistance  $(R_{\text{ON,sp}})$  of 0.36 m $\Omega \cdot \text{cm}^2$  (normalized by the active fin area) and 800-V blocking voltage.  $R_{\rm ON,sp}$  was 3.24 m $\Omega \cdot \rm cm^2$  if normalized by the total device area. Zhang et al. [23] further demonstrated GaN fin MOSFETs with BV of 1.2 kV and  $R_{\text{ON,sp}}$  of 0.2 m $\Omega \cdot \text{cm}^2$  (normalized by the active fin area).  $R_{\text{ON,sp}}$  was 1 m $\Omega \cdot \text{cm}^2$  if normalized by the total device area. Zhang et al. [23] also demonstrated large-area devices with ON-current of 5 A and  $R_{ON,sp}$  of 2.1 m $\Omega \cdot cm^2$  (normalized by the total device area). The only experimentally reported VC-JFETs by Kotzea et al. [24] showed very weak gate modulation effects with a large leakage and a drain current ON/OFF ratio of less than 2. The poor device performance is partly due to limited understanding of nonideal effects during regrowth on fin-like channels.

In this work, we designed and fabricated the GaN VC-JFETs on bulk GaN substrates by metalorganic chemical vapor deposition (MOCVD). The p-GaN gates were regrown on GaN epilayers with fin-like channels patterned by electron beam lithography (EBL). A maskless blanket regrowth and a subsequent self-planarization process were applied to define the p-GaN gate regions. GaN VC-JFETs with a decent ON/OFF ratio of ~100 and very high transconductance of over 600 S/cm<sup>2</sup> were achieved, which are considerable improvements over previous reports. The nonideal factors that limit the device performance during regrowth were also analyzed by secondary ion mass spectroscopy (SIMS) and cathodoluminescence (CL).

## **II. DEVICE STRUCTURE AND FABRICATION**

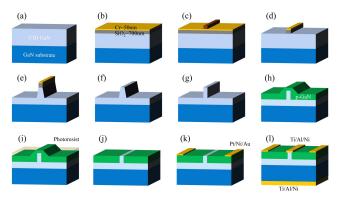

The device epilayers were grown by MOCVD where trimethylgallium (TMGa) served as the Ga precursor and ammonia (NH<sub>3</sub>) was the source for nitrogen. The carrier gas was hydrogen (H<sub>2</sub>). Fig. 2 shows the growth and fabrication process of the GaN VC-JFETs. A  $4-\mu$ m-thick unintentionally doped (UID) GaN was homoepitaxially grown on heavily doped bulk GaN substrates. The background electron

Fig. 2. Fabrication process of the VC-JFET. (a) Epilayer growth. (b) Cr and SiO<sub>2</sub> hard masks deposition. (c) E-beam lithography. (d) ICP etching to define hard masks. (e) Two-step ICP etching. (f) Hard masks removal. (g) TMAH wet etching. (h) p-GaN regrowth. (i) Photoresist assisted planarization. (j) Top p-GaN etching. (k) Gate metal contacts deposition. (I) Source and drain metal contacts deposition.

density was estimated to be  $\sim 10^{16}$  cm<sup>-3</sup> by capacitancevoltage (C-V) measurement. Cr (50 nm)/SiO<sub>2</sub> (700 nm) were deposited as hard masks for fin patterns that were transferred by EBL. The chlorine- and fluorine-based reactive ion etchings (RIEs) were used to etch Cr and SiO<sub>2</sub> hard masks, respectively. To improve the regrowth surface, the fins were formed by a two-step inductively coupled plasma (ICP) etching: a 6-min high-RF-power fast etching (~280 nm/min) and a 3-min low-RF-power slow etching (~20 nm/min). Our previous results showed that low RF power ICP etching can improve the performance of regrown planar p-n junctions [25]. The hard mask residuals (Cr and SiO<sub>2</sub>) were removed by Cr etchant and hydrofluoric (HF) acid. The samples were then dipped in 75 °C 25% hot tetramethylammonium hydroxide (TMAH) for 5 min to further recover etching damages created by ion bombardments during ICP etching. The samples were then immersed in piranha for 15 min to further remove possible organic contaminants [26]. The samples were then treated by UV-ozone for 1 h, followed by a buffered oxide etch (BOE) and 10% hydrochloric (HCl) acid for 5 min, respectively, to remove surface charges. Finally, the thoroughly cleaned samples were immediately reloaded into the MOCVD chamber for p-GaN regrowth. A 1  $\mu$ m p-GaN with an Mg concentration of 10<sup>19</sup> cm<sup>-3</sup> was regrown on the sample using bis(cyclopentadienyl)magnesium (Cp2Mg) as the Mg precursor. After the regrowth, acceptor activation of the regrown p-GaN was conducted at 700 °C for 20 min in a nitrogen environment. A photoresist-based planarization process was used to selectively etch away the p-GaN on top of the fin and expose n-GaN for source contacts. Gate electrodes were formed by Pd/Ni/Au (30/20/100 nm) by electron beam evaporation and then annealed at 450 °C for 5 min in a nitrogen ambient. Finally, the source and drain electrodes Ti/Al/Ni (30/100/30 nm) were deposited by electron beam evaporation.

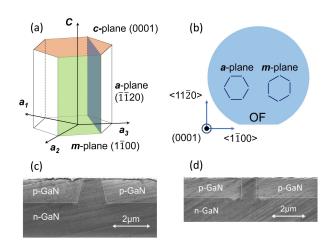

The VC-JFET devices with fins aligned to either a-plane or m-plane were fabricated. Fig. 3(a) shows the schematic of the GaN crystal planes. The alignment direction relative to the orientation flat (OF) is shown in Fig. 3(b). The wet etching of TMAH in GaN is strongly anisotropic, which results in different sidewall profiles for the two different

Fig. 3. (a) Crystal planes in GaN wurtzite structure. (b) Schematics of the fin alignment direction. SEM cross-sectional images of the VC-JFETs in (c) *a*-plane and (d) *m*-plane.

Fig. 4. Schematics of the cross section of GaN VC-JFETs.

crystal orientations [27]. The device aligned to the *m*-plane in Fig. 3(d) shows a narrower and more vertical fin than that the device aligned to *a*-plane in Fig. 3(c).

#### **III. RESULTS AND DISCUSSION**

## A. Regrowth Verification

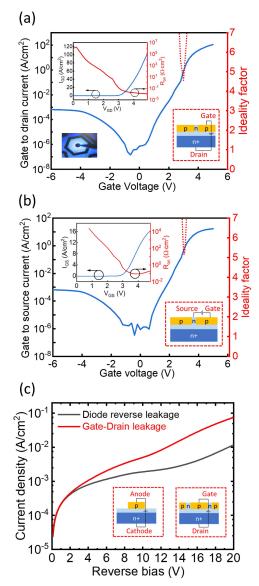

In the GaN VC-JFETs, two types of p-n junctions were formed by the p-GaN regrowth: the lateral and vertical p-n junctions, as shown in Fig. 4. The former was the junction between the gate and the source, and the latter was the junction between the gate and the drain. The junctions shared the same gate electrode that was attached to p-GaN. The n-contacts for the lateral and vertical p-n junctions are formed on the exposed fin (~960  $\mu$ m<sup>2</sup>) and the backside of the wafer, respectively. The currents were normalized by the gate electrode area, which is  $\sim 1 \times 10^5 \ \mu m^2$ . The current–voltage (I-V) characteristics of the two p-n junctions were measured by a Keithley 2410 source meter. Fig. 5(a) and (b) shows the representative I-V curves of the vertical and lateral p-n junctions, respectively. Similar forward rectifying characteristics with an ON/OFF ratio of  $\sim 10^5$  were observed for both junctions. At forward bias, strong electroluminescence (EL) was observed, which indicates that the p-GaN regrowth was effective. The turn-on voltages, as extracted from linear extrapolation, were 3.4 and 3.1 V in the vertical and lateral p-n junctions, respectively. This larger turn-on voltage of the vertical p-n junction is likely due to the thicker n-GaN layer in the vertical direction. The two junctions showed abnormal ideality factors of over 4. This is likely caused by the regrowth

Fig. 5. (a)  $\vdash V$  curves for the vertical p-n junctions between the gate and the drain. (b)  $\vdash V$  curves for the lateral p-n junctions between the gate and the source. The insets show schematics of the p-n junctions in GaN VC-JFETs. (c) Reverse leakage current of a planar diode and a p-n junction between the gate and the drain.

process since defects, etching damage, and impurities can serve as nonradiative recombination centers at the regrowth interfaces, thus increasing ideality factors. The lateral and vertical p-n junctions show similar leakage currents, which are further compared with previous reports. The leakage currents in this work are comparable to the reported regrown p-n junctions and not surprisingly larger than as-grown vertical p-n diodes [28]. In this work, the p-GaN layer was directly regrown on UID-GaN. It was reported that introducing an undoped insertion layer may move the surface impurities away from p-GaN and reduce the leakage in the regrown p-n junctions [25], which is an on-going topic.

To understand leakage paths for the regrown p-n junctions, the reverse leakage characteristics of a planar diode (without fins) and a vertical p-n junction between the gate and the drain (with fins) on the same wafer are compared in Fig. 5(c). Both p-n diodes show larger leakage currents compared with

Fig. 6. Device electrical properties. (a) Representative  $I_D - V_{GS}$  transfer characteristics in a linear scale. (b) Representative  $I_D - V_{DS}$  output characteristics.

as-grown diodes. The discrepancy between the two diodes becomes larger at higher reverse bias. This suggests that both nonpolar and polar regrowth interfaces contribute to the leakage current. The total leakage is the superposition of leakage currents from all etched surfaces. The *c*-plane interface may be dominant at a low bias (<2 V), and the leakage current through nonpolar planes increases with increasing reverse bias. The leakage currents continue to increase after 10 V with no sign of saturation.

### B. VC-JFET Characteristics

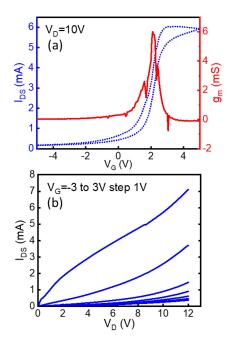

The transistor characteristics were measured by a Keithley 4200 SCS parameter analyzer. The effective area for the source region is 960  $\mu$ m<sup>2</sup>, consisting of six fins each with an area of 1  $\mu$ m × 160  $\mu$ m. The total device area, including the source/gate electrode areas, is ~2.5×10<sup>5</sup>  $\mu$ m<sup>2</sup>. Fig. 6(a) shows the transfer characteristics of the VC-JFET with fins aligned to *m*-plane. At a drain voltage of 10 V, the ON/OFF ratio is ~100, which is much higher than the previous report (which is less than 2) [24]. As the gate voltage increased to 2.2 V, the gate current begun to increase due to the turn-on of the gate to source p-n junction, and as a result, the drain current slightly decreased. A hysteresis of ~0.4 V was observed in the  $I_D-V_{GS}$  transfer curve due to charges at the regrowth interface.

Fig. 6(b) shows the output  $I_D-V_{\rm DS}$  family curves. Gate modulation was obtained, but no current saturation was observed in the VC-JFET mainly due to gate leakage. The drain current density reached 740 A/cm<sup>2</sup> with an  $R_{\rm ON,sp}$  of 10.5 m $\Omega \cdot \rm cm^2$  (normalized by the fin area) at a  $V_G$  bias of 3 V and  $V_{\rm DS}$  bias of 12 V. The ON-resistance normalized by the total device region is 2.8  $\Omega \cdot \rm cm^2$ . Since nonalloyed contacts for the source and the drain were used, thermal annealing may further decrease the ON-resistance.

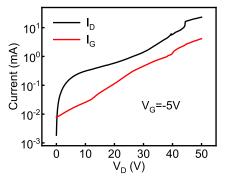

Typical OFF-state  $I_D$ ,  $I_G-V_D$  curves of the GaN VC-JFETs are shown in Fig. 7. The gate current was mainly the

Fig. 7. Representative OFF-state characteristics of the VC-JFETs.

Fig. 8. Transfer characteristics of VC-JFETs aligned to different crystal orientations: (a) *m*-plane and (b) *a*-plane.

superposition of leakage current from both lateral and vertical p-n junctions. The drain current consists of leakage current from vertical p-n junctions and the leakage current induced by the weak pinch-off effects of lateral p-n junctions. The drain current is around ten times higher than the gate current, indicating the drain leakage contributed to the main leakage in drain current at the OFF-state. The drain current broke down at 45 V, while no breakdown was observed at the gate. These results suggest that the OFF-state characteristics of this device are primarily limited by weak pinch-off effects of the lateral p-n junctions.

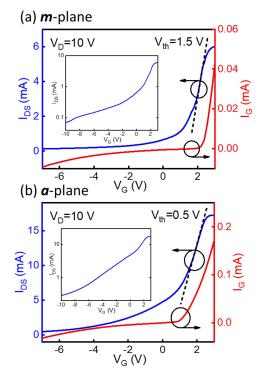

## C. Comparison of a-plane and m-plane Devices

Fig. 8(a) and (b) compares the transfer characteristics of the VC-JFETs aligned to *m*-plane and *a*-plane, respectively. The peak transconductances are 625 and 916 S/cm<sup>2</sup> (normalized by fin areas) in *m*-plane and *a*-plane devices, respectively, [29]–[33]. The threshold voltages ( $V_{\text{th}}$ ) are determined by the following method: first, the point of maximum transconductance on the  $I_D-V_{\text{GS}}$  curve was found, and the maximum slope was extrapolated to  $I_{DS} = 0$  to find the *x*-axis intercept. The *m*-plane and the *a*-plane devices showed turn-on voltages at ~1.5 and ~0.5 V, respectively.

The *a*-plane device showed higher ON-current compared to the m-plane. This discrepancy is likely due to nonalloyed source contacts. The UID-GaN was treated with ICP etching to created donor-like surface defects to facilitate drain contacts [34]. While different surface conditions before electrode deposition may lead to nonuniform contact resistance in different devices, the gate leakage in the *a*-plane devices is around ten times higher than that of the *m*-plane devices. This difference in gate leakage is likely related to different crystal orientations. It has been shown that m-plane sidewalls are much smoother than the *a*-plane after TMAH treatment [35]. A recent study also shows that GaN vertical MOSFETs with trenches aligned to the m-plane present better performance than a-plane [33]. It is possible that the defect and impurity level at *m*-plane could be lower than *a*-plane after TMAH treatment, resulting in lower gate leakage.

#### D. Nonideal Factors in Regrowth

Interfacial impurities, such as silicon (Si) and oxygen (O), have been shown to strongly affect GaN regrown p-n diodes [36], [37]. In our previous study under the same growth condition, it was observed that there were high levels of positively charged donors at the regrowth interface. These donors were attributed to Si ( $\sim 10^{19}$  cm<sup>-3</sup>) and O ( $\sim 10^{17}$  cm<sup>-3</sup>) at the *c*-plane according to the SIMS results [28]. Such high levels of impurities were also observed at m-plane regrown interfaces [38]. Using electron holography, the electrostatic potential profile at the regrowth interface was obtained. The energy band diagram showed a large band bending at the regrowth interface. This indicates the formation of a p<sup>+</sup>/n<sup>+</sup> tunneling junction at the regrowth interface. n<sup>+</sup>-GaN is due to a high concentration of Si and O impurities acting as shallow donors, and the  $p^+$  doping at the regrowth interface is likely due to Si-Mg and/or O-Mg codoping effects. Research has shown that the overlapping of Mg and Si/O at the interface region can enhance the hole concentration up to two orders of magnitude [39]. The formation of tunneling junctions at the regrowth interface is likely to be responsible for the large leakage, premature breakdown in regrown p-n junctions, and weak pinch-off effect of the lateral p-n junctions. More in-depth analysis of the effects of impurities and electron holography can be found in [40]. Recently, Xiao et al. [41] reported that Mg preflow before p-GaN growth can compensate for the interfacial Si/O impurities. This method is promising in enhancing the regrown junction blocking capabilities.

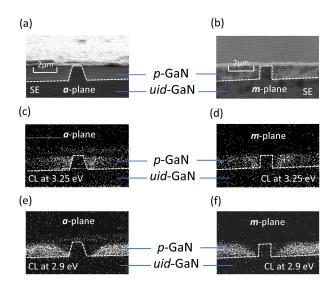

Another factor limiting the device performance is the nonuniform distribution of acceptors in GaN epilayers grown on fin structures. CL spectroscopy was used to study the optical properties of p-GaN in VC-JFET devices. The CL was carried out in a JEOL 6300 scanning electron microscope. The electron beam current used in this study was 100 pA, and the acceleration voltage was 7 kV. CL mappings were obtained by recording the spatial variation of luminescence intensity over an area at a certain wavelength. Fig. 9 shows the secondary electron (SE) images and CL mappings at 3.25 and 2.9 eV of

Fig. 9. Cross-sectional view of the VC-JFETs devices: SE images of devices aligned to (a) *a*-plane and (b) *m*-plane. Monochromatic CL images at 3.25 eV for devices aligned to (c) *a*-plane and (d) *m*-plane. Monochromatic CL images at 2.9 eV for devices aligned to (e) *a*-plane (f) *m*-plane.

m- and a-plane devices. According to [18], 2.9-eV emission intensity in CL can be used as an indicator of acceptor concentrations. The higher the CL intensity at 2.9 eV, the higher the acceptor concentration. It is clear in Fig. 9(e) and (f) that weaker intensity was observed on the sidewalls of the fins, indicating that the p-GaN grown on the sidewall of the fins had lower acceptor concentration. This can adversely impact the device performance since the fin channel will be more difficult to be pinched off due to weaker depletion effects in the channel at lower acceptor concentrations. This could make it more difficult to achieve enhancement mode in VC-JFETs. The interface between acceptor-deficient p-GaN and normal p-GaN makes a  $45^{\circ}$  angle with the basal plane in both *m*- and a-plane devices. This indicates that this phenomenon is not related to crystal orientations and possibly due to regrowth conditions and/or surface treatment.

All the aforementioned nonideal factors indicate that device regrowth with trenches is much more complicated and difficult than regrowth on planar surfaces. To achieve complete pinch-off in channels, the tunneling junctions at the regrowth interface must be eliminated. Methods are needed to simultaneously remove or compensate impurities on the *c*-plane and nonpolar surfaces, as nonpolar planes have very different material properties from the polar *c*-planes, such as dangling bond densities, surface states, and impurities incorporation. In addition, to realize normally-OFF operation, regrowth conditions (e.g., temperature, pressure, and III/V ratio) also need to be optimized to improve acceptor concentrations at the sidewall.

#### **IV. CONCLUSION**

We experimentally demonstrated GaN VC-JFETs through p-GaN regrowth on the patterned fin-like channel regions by MOCVD. A subsequent photoresist self-planarization process was applied to etch away the p-GaN on top of the n-GaN fins. The regrown lateral and vertical p-n junctions were characterized to verify the effectiveness of the regrowth process. The VC-JFETs show an ON-OFF ratio  $\sim 100$  and excellent transconductances. Devices with vertical channels aligned to a-plane and m-plane were also compared. The nonideal factors, such as interfacial impurities and nonuniform acceptor distribution, were also discussed. The follow-up work on minimizing leakage currents and improving BVs is underway.

#### REFERENCES

- [1] Y. Zhao, H. Fu, G. T. Wang, and S. Nakamura, "Toward ultimate efficiency: Progress and prospects on planar and 3D nanostructured nonpolar and semipolar InGaN light-emitting diodes," Adv. Opt. Photon., vol. 10, no. 1, pp. 246-308, Feb. 2018, doi: 10.1364/AOP.10.000246.

- [2] H. Fu, Z. Lu, and Y. Zhao, "Analysis of low efficiency droop of semipolar InGaN quantum well light-emitting diodes by modified rate equation with weak phase-space filling effect," AIP Adv., vol. 6, no. 6, p. 65013, Jun. 2016, doi: 10.1063/1.4954296.

- [3] J. Y. Tsao et al., "Ultrawide-bandgap semiconductors: Research opportunities and challenges," Adv. Electron. Mater., vol. 4, no. 1, Jan. 2018, Art. no. 1600501, doi: 10.1002/aelm.201600501.

- [4] H. Chen et al., "Characterizations of nonlinear optical properties on GaN crystals in polar, nonpolar, and semipolar orientations," Appl. Phys. Lett., vol. 110, no. 18, May 2017, Art. no. 181110, doi: 10.1063/1.4983026.

- [5] E. A. Jones, F. F. Wang, and D. Costinett, "Review of commercial GaN power devices and GaN-based converter design challenges," IEEE J. Emerg. Sel. Topics Power Electron., vol. 4, no. 3, pp. 707-719, Sep. 2016, doi: 10.1109/JESTPE.2016.2582685.

- [6] H. Fu et al., "High voltage vertical GaN p-n diodes with hydrogenplasma based guard rings," IEEE Electron Device Lett., vol. 41, no. 1, pp. 127-130, Jan. 2020, doi: 10.1109/LED.2019.2954123.

- [7] H. Amano et al., "The 2018 GaN power electronics roadmap," J. Phys. D, Appl. Phys., vol. 51, no. 16, Apr. 2018, Art. no. 163001, doi: 10.1088/1361-6463/aaaf9d.

- [8] H. Fu, X. Huang, H. Chen, Z. Lu, I. Baranowski, and Y. Zhao, "Ultralow turn-on voltage and on-resistance vertical GaN-on-GaN Schottky power diodes with high mobility double drift layers," Appl. Phys. Lett., vol. 111, no. 15, Oct. 2017, Art. no. 152102, doi: 10.1063/1. 4993201

- [9] R. D. Underwood, D. Kapolnek, B. P. Keller, S. Keller, S. P. Denbaars, and U. K. Mishra, "Selective-area regrowth of GaN field emission tips," Solid-State Electron., vol. 41, pp. 243-245, Feb. 1997, doi: 10.1016/ S0038-1101(96)00209-2.

- [10] B. S. Shelton et al., "Selective area growth and characterization of AlGaN/GaN heterojunction bipolar transistors by metalorganic chemical vapor deposition," IEEE Trans. Electron Devices, vol. 48, no. 3, pp. 490-494, Mar. 2001, doi: 10.1109/16.906441.

- [11] H. Nie et al., "1.5-kV and 2.2-mΩ-cm<sup>2</sup> vertical GaN transistors on bulk-GaN substrates," IEEE Electron Device Lett., vol. 35, no. 9, pp. 939-941, Sep. 2014, doi: 10.1109/LED.2014.2339197.

- [12] A. Debald, S. Kotzea, M. Heuken, H. Kalisch, and A. Vescan, "Growth and characterization of vertical and lateral p-n junctions formed by selective-area p-GaN MOVPE on patterned templates," Phys. Status Solidi A, vol. 216, no. 2, Jan. 2019, Art. no. 1800677, doi: 10.1002/pssa. 201800677

- [13] Y.-T. Shi et al., "Realization of p-type gallium nitride by magnesium ion implantation for vertical power devices," Sci. Rep., vol. 9, no. 1, p. 8796, Dec. 2019, doi: 10.1038/s41598-019-45177-0.

- [14] T. Niwa, T. Fujii, and T. Oka, "High carrier activation of Mg ionimplanted GaN by conventional rapid thermal annealing," Appl. Phys. Express, vol. 10, no. 9, p. 91002, 2017, doi: 10.7567/apex.10.091002.

- [15] T. Narita, T. Kachi, K. Kataoka, and T. Uesugi, "P-type doping of GaN (0001) by magnesium ion implantation," Appl. Phys. Express, vol. 10, no. 1, p. 16501, 2016, doi: 10.7567/apex.10.016501.

- [16] M. Yoshino, K. Sugamata, K. Ikeda, T. Nishimura, K. Kuriyama, and T. Nakamura, "Ion implanted GaN MISFETs fabricated in Mg implanted layers activated by conventional rapid thermal annealing," Nucl. Instrum. Methods Phys. Res. Sect. B, Beam Interact. Mater. At., vol. 449, pp. 49-53, Jun. 2019, doi: 10.1016/j.nimb.2019.04.008

- [17] S. C. Cruz, S. Keller, T. E. Mates, U. K. Mishra, and S. P. DenBaars, "Crystallographic orientation dependence of dopant and impurity incorporation in GaN films grown by metalorganic chemical vapor deposition," J. Cryst. Growth, vol. 311, no. 15, pp. 3817-3823, Jul. 2009, doi: 10.1016/j.jcrysgro.2009.02.051.

- [18] H. Liu et al., "Non-uniform Mg distribution in GaN epilayers grown on mesa structures for applications in GaN power electronics," Appl. Phys. Lett., vol. 114, no. 8, p. 82102, Feb. 2019, doi: 10.1063/1.5088168.

- [19] Z. Hu et al., "1.1-kV vertical GaN p-n diodes with p-GaN regrown by molecular beam epitaxy," IEEE Electron Device Lett., vol. 38, no. 8, pp. 1071-1074, Aug. 2017, doi: 10.1109/LED.2017.2720747.

- [20] Y. Zhang and T. Palacios, "(Ultra) wide-bandgap vertical power Fin-FETs," IEEE Trans. Electron Devices, early access, Jun. 24, 2020, doi: 10.1109/TED.2020.3002880.

- [21] D. Ji and S. Chowdhury, "Design of 1.2 kV power switches with low R<sub>ON</sub> using GaN-based vertical JFET," IEEE Trans. Electron Devices, vol. 62, no. 8, pp. 2571-2578, Aug. 2015, doi: 10.1109/TED.2015.2446954

- [22] M. Sun, Y. Zhang, X. Gao, and T. Palacios, "High-performance GaN vertical fin power transistors on bulk GaN substrates," IEEE Electron Device Lett., vol. 38, no. 4, pp. 509-512, Apr. 2017, doi: 10.1109/LED. 2017 2670925

- [23] Y. Zhang et al., "Large-area 1.2-kV GaN vertical power FinFETs with a record switching figure of merit," IEEE Electron Device Lett., vol. 40, no. 1, pp. 75-78, Jan. 2019, doi: 10.1109/LED.2018.2880306.

- [24] S. Kotzea, A. Debald, M. Heuken, H. Kalisch, and A. Vescan, "Demonstration of a GaN-based vertical-channel JFET fabricated by selective-area regrowth," IEEE Trans. Electron Devices, vol. 65, no. 12, pp. 5329-5336, Dec. 2018, doi: 10.1109/TED.2018.2875534

- [25] K. Fu et al., "Demonstration of 1.27 kV etch-then-regrow GaN p - n junctions with low leakage for GaN power electronics," IEEE Electron Device Lett., vol. 40, no. 11, pp. 1728-1731, Nov. 2019, doi: 10.1109/LED.2019.2941830.

- [26] Y. Zhang et al., "Trench formation and corner rounding in vertical GaN power devices," Appl. Phys. Lett., vol. 110, no. 19, May 2017, Art. no. 193506, doi: 10.1063/1.4983558. [27] M. Kodama *et al.*, "GaN-based trench gate metal oxide semiconductor

- field-effect transistor fabricated with novel wet etching," Appl. Phys. Express, vol. 1, no. 2, p. 21104, 2008, doi: 10.1143/apex.1.021104.

- [28] K. Fu et al., "Investigation of GaN-on-GaN vertical p-n diode with regrown p-GaN by metalorganic chemical vapor deposition," Appl. Phys. Lett., vol. 113, no. 23, Dec. 2018, Art. no. 233502, doi: 10.1063/1.5052479.

- [29] C. Liu, R. A. Khadar, and E. Matioli, "GaN-on-Si quasi-vertical power MOSFETs," IEEE Electron Device Lett., vol. 39, no. 1, pp. 71-74, Jan. 2018, doi: 10.1109/LED.2017.2779445.

- [30] C. Gupta et al., "In situ oxide, GaN interlayer-based vertical trench MOSFET (OG-FET) on bulk GaN substrates," IEEE Electron Device Lett., vol. 38, no. 3, pp. 353-355, Mar. 2017, doi: 10.1109/LED.2017. 2649599

- [31] R. Li, Y. Cao, M. Chen, and R. Chu, "600 V/ 1.7 Ω normally-off GaN vertical trench metal-oxide-semiconductor field-effect transistor," IEEE Electron Device Lett., vol. 37, no. 11, pp. 1466-1469, Nov. 2016.

- [32] D. Ji et al., "Large-area in-situ oxide, GaN interlayer-based vertical trench MOSFET (OG-FET)," IEEE Electron Device Lett., vol. 39, no. 5, pp. 711-714, May 2018, doi: 10.1109/LED.2018.2813312

- [33] R. A. Khadar, C. Liu, R. Soleimanzadeh, and E. Matioli, "Fully vertical GaN-on-Si power MOSFETs," IEEE Electron Device Lett., vol. 40, no. 3, pp. 443-446, Mar. 2019, doi: 10.1109/LED.2019.2894177.

- [34] H. W. Jang and J.-L. Lee, "Effect of Cl2 plasma treatment on metal contacts to n-type and p-type GaN," J. Electrochem. Soc., vol. 150, no. 9, pp. G513-G519, 2003, doi: 10.1149/1.1595664.

- [35] J. He et al., "On-wafer fabrication of cavity mirrors for InGaN-based laser diode grown on Si," Sci. Rep., vol. 8, no. 1, p. 7922, Dec. 2018, doi: 10.1038/s41598-018-26305-8.

- A. Aragon et al., "Interfacial impurities and their electronic signatures [36] in high-voltage regrown nonpolar m-plane GaN vertical p-n diodes," Phys. Status Solidi A, vol. 217, no. 7, Dec. 2019, Art. no. 1900757, doi: 10.1002/pssa.201900757.

- [37] K. Fu et al., "Reverse leakage analysis for as-grown and regrown vertical GaN-on-GaN Schottky barrier diodes," IEEE J. Electron Devices Soc., vol. 8, pp. 74-83, Jan. 2020. [Online]. Available: https://ieeexplore. ieee.org/document/8949530, doi: 10.1109/JEDS.2020.2963902.

- [38] M. Monavarian et al., "High-voltage regrown nonpolar m -plane vertical p-n diodes: A step toward future selective-area-doped power switches,' IEEE Electron Device Lett., vol. 40, no. 3, pp. 387-390, Mar. 2019, doi: 10.1109/LED.2019.2892345.

- [39] H. Katayama-Yoshida, T. Nishimatsu, T. Yamamoto, and N. Orita, "Codoping method for the fabrication of low-resistivity wide bandgap semiconductors in p-type GaN, p-type AlN and n-type diamond: Prediction versus experiment," J. Phys., Condens. Matter, vol. 13, no. 40, pp. 8901-8914, Oct. 2001, doi: 10.1088/0953-8984/13/40/304.

- [40] S. R. Alugubelli et al., "Determination of electronic band structure by electron holography of etched-and-regrown interfaces in GaN p-i-n diodes," Appl. Phys. Lett., vol. 115, no. 20, Nov. 2019, Art. no. 201602, doi: 10.1063/1.5127014.

- [41] M. Xiao et al., "Lateral p-GaN/2DEG junction diodes by selectivearea p-GaN trench-filling-regrowth in AlGaN/GaN," Appl. Phys. Lett., vol. 116, no. 5, p. 53503, Feb. 2020, doi: 10.1063/1.5139906.